随着摩尔定律的失效,基于半导体集成电路的信息技术已逐步逼近物理极限,后摩尔时代的信息技术亟待全新的范式和原理。现代计算机自问世以来一直采用冯诺依曼结构,即运算器与存储器分离,这种结构使得运算器与存储器之间的数据传输成为影响系统性能的瓶颈(称为冯诺依曼瓶颈),大大限制了计算机性能的提高;同时,由于现代计算机中的运算器和主存储器(如DRAM)都是易失性器件,不仅在断电后信息立即消失,而且具有较高的能耗。因此,开发新型非易性器件,采用非冯诺依曼结构,实现运算器和存储器合二为一(logic in memory),是未来发展高性能、低功耗、即开即用型计算机要解决的关键问题。当前,忆阻器(memristor)作为一种非易失性器件,由于同时具有信息存储和逻辑运算功能,有望在未来替代半导体晶体管,受到了学术界和工业界的广泛关注。

近期,中国科学院物理研究所磁学国家重点实验室孙阳研究员、尚大山副研究员和柴一晟副研究员等提出了另一种非易失性器件—忆耦器(memtranstor),并在单个忆耦器上分别实现了两态存储、多态存储和布尔逻辑运算。忆耦器是一种基于非线性磁电耦合效应的记忆元件,源于第四种基本电路元件电耦器(transtor)。忆耦器的基本特征是其表现出非线性电荷-磁通回滞曲线。与忆阻器采用电阻(R = dv/di)的状态存储信息不同,忆耦器采用电耦(T = dq/dφ,或者等效于磁电耦合系数 α= dE/dH)的状态来存储信息。忆耦器的信息处理原理采用电写磁读,具有高速度、高密度、低功耗、并行读取、结构简单、易于制备等优点。

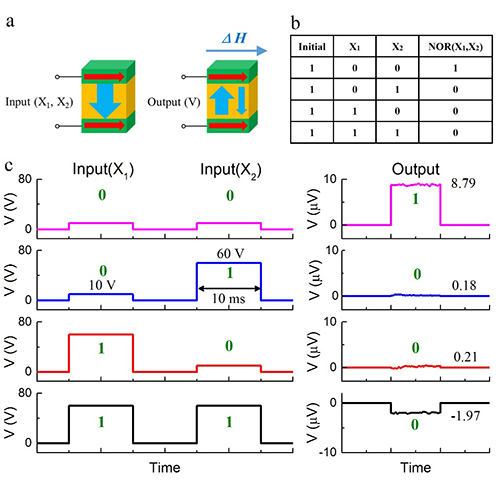

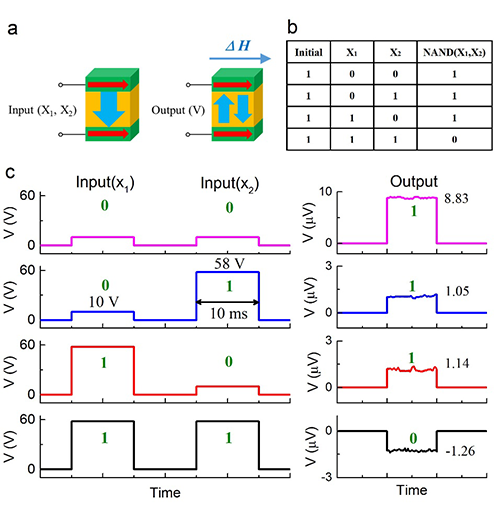

孙阳研究组的研究生申见昕、丛君状和申世鹏等分别基于多种磁电耦合介质制备了几种忆耦器。他们首先在Ag/PMN-PT/Terfenol-D/Ag忆耦器中实现了室温下两态信息存储,第一次演示了忆耦器作为新型非易失性存储器的功能 [以Letter形式发表于Phys. Rev. Applied 6, 021001 (2016)]。在此基础上,他们又在该忆耦器中实现了多态(4态和8态)存储。常规存储器每个存储单元只能存储2种状态(0, 1),而多态存储器在每个存储位上可以存储2n个状态,因而具有更高的存储密度。与电阻型多态存储器相比,由于电耦值可以从正到负分布,因而忆耦器具有更高的存储密度和容错度。此后,他们采用简单金属Ni来替代复杂贵重合金Terfenol-D (Tb0.28Dy0.72Fe1.95),制备了Ni/PMN-PT/Ni忆耦器,实现了非易失性两态和多态存储器。更为重要的是,他们基于单个Ni/PMN-PT/Ni忆耦器实现了非易失性通用逻辑门NOR和NAND。这一成果表明忆耦器与忆阻器类似,可以兼有信息存储和布尔逻辑运算的功能,因而有望用于实现非冯诺依曼结构的下一代计算机。此外,研究生鲁佩佩等基于有机铁电体制备出Cu/P(VDF-TrFE)/Metglas和Cu/P(VDF-TrFE)/Ni有机忆耦器,并成功实现了非易失性多态信息存储。有机忆耦器有望在未来用于柔性可穿戴电子器件。

这些系列研究进展表明,忆耦器在开发下一代信息功能器件方面具有巨大的潜力。与目前人们广泛关注的忆阻器相比,忆耦器具有更低功耗和并行信息处理等优点。以上研究成果分别发表于Phys. Rev. Applied 6, 021001 (2016);Phys. Rev. Applied 6, 064028 (2016);Sci. Rep. 6, 34473 (2016);Appl. Phys. Lett. 109, 252902 (2016)。在2016年11月于美国新奥尔良举行的第61届国际磁学与磁性材料大会(MMM)上,孙阳研究组关于忆耦器的工作被评为大会最佳张贴报告奖(Best Poster Award),是中国地区(包括台湾、香港和澳门)唯一获得该奖项的工作。

该研究获得了国家自然科学基金、科技部和中国科学院项目的支持。

相关文章链接:

1. http://journals.aps.org/prapplied/abstract/10.1103/PhysRevApplied.6.021001

2. http://journals.aps.org/prapplied/abstract/10.1103/PhysRevApplied.6.064028

3. http://www.nature.com/articles/srep34473

4. http://aip.scitation.org/doi/full/10.1063/1.4972304

|

| 图1. 忆耦器的结构和原理示意图。通过施加电压改变磁电耦合系数的状态来写入信息,通过施加磁场来并行读取信息。 |

|

| 图2. 基于忆耦器实现非易失性多态存储器。 |

|

| 图3. 基于忆耦器实现非易失性逻辑门NOR。 |

|

| 图4. 基于忆耦器实现非易失性逻辑门NAND。 |