# Implementation of complete Boolean logic functions in single spin–orbit torque device

Cite as: AIP Advances **11**, 015045 (2021); https://doi.org/10.1063/5.0030016 Submitted: 18 September 2020 . Accepted: 28 December 2020 . Published Online: 27 January 2021

🔟 Yunchi Zhao, 🔟 Guang Yang, Jianxin Shen, 🔟 Shuang Gao, ២ Jingyan Zhang, Jie Qi, Haochang Lyu, 匝 Guogiang Yu, 🔟 Kui Jin, and Shouguo Wang

## COLLECTIONS

Paper published as part of the special topic on Chemical Physics, Energy, Fluids and Plasmas, Materials Science and Mathematical Physics

# **ARTICLES YOU MAY BE INTERESTED IN**

Field-free switching of magnetic tunnel junctions driven by spin-orbit torques at sub-ns timescales

Applied Physics Letters 116, 232406 (2020); https://doi.org/10.1063/5.0011433

Probing edge condition of nanoscale CoFeB/MgO magnetic tunnel junctions by spin-wave resonance

Applied Physics Letters 117, 202404 (2020); https://doi.org/10.1063/5.0020591

Large damping-like spin-orbit torque and perpendicular magnetization switching in sputtered  $WTe_X$  films

Applied Physics Letters 118, 042401 (2021); https://doi.org/10.1063/5.0035681

AIP Advances Fluids and Plasmas Collection

# Implementation of complete Boolean logic functions in single spin-orbit torque device

Cite as: AIP Advances 11, 015045 (2021); doi: 10.1063/5.0030016 Submitted: 18 September 2020 • Accepted: 28 December 2020 • Published Online: 27 January 2021

Yunchi Zhao,<sup>1,2</sup> D Guang Yang,<sup>3,a)</sup> Jianxin Shen,<sup>4</sup> Shuang Gao,<sup>5</sup> D Jingyan Zhang,<sup>4</sup> Jie Qi,<sup>4</sup> Haochang Lyu,<sup>4</sup> Guoqiang Yu,<sup>1,2</sup> Kui Jin,<sup>1,2</sup> Rui Jin,<sup>1,2</sup> Rui Shouguo Wang<sup>4,a)</sup>

#### **AFFILIATIONS**

<sup>1</sup>Beijing National Laboratory for Condensed Matter Physics, Institute of Physics, Chinese Academy of Sciences, Beijing 100190, China

<sup>2</sup>School of Physical Sciences, University of Chinese Academy of Sciences, Beijing 100049, China

- <sup>3</sup>Department of Materials Science and Metallurgy, University of Cambridge, 27 Charles Babbage Road, Cambridge CB3 0FS, United Kingdom

- <sup>4</sup>Beijing Advanced Innovation Center for Materials Genome Engineering, School of Materials Science and Engineering, University of Science and Technology Beijing, Beijing 100083, China

- <sup>5</sup>CAS Key Laboratory of Magnetic Materials and Devices, Ningbo Institute of Materials Technology and Engineering, Chinese Academy of Sciences, Ningbo 315201, China

<sup>a)</sup>Authors to whom correspondence should be addressed: gy251@cam.ac.uk and sgwang@ustb.edu.cn

#### ABSTRACT

All 16 Boolean logic functions in a single Ta/CoFeB/MgO device with perpendicular magnetic anisotropy were experimentally demonstrated based on the spin–orbit torque (SOT) effect. Furthermore, by combining with the voltage-controlled magnetic anisotropy (VCMA) effect, a novel SOT-MTJ (magnetic tunnel junction) prototype device with the assistance of the VCMA effect was further designed to perform magnetic field-independent logic operations. The numerical simulations were carried out, demonstrating the feasibility to realize all 16 Boolean logic functions in a single three-terminal device by applying the bias voltage and current injection as input variables. This approach provides a potential way toward the application of energy efficient spin-based logic, which is beyond the current von Neumann computing architecture.

© 2021 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/5.0030016

The continued scaling of complementary metal-oxidesemiconductor (CMOS) technology according to Moore's law has brought to us upgraded electronic devices with a smaller volume, higher speed, and lower price for decades. However, the challenge to such rapid development still exists.<sup>1,2</sup> One critical limitation is the explosive growth of static power dissipation arising from the leakage current as the CMOS feature size scales down to a few nanometers.<sup>3</sup> On the other hand, the operating speed of electronic devices is seriously limited by the ineluctable data exchange between separate processor and memory units, encountering the so-called von Neumann bottleneck that further brings massive dynamic power dissipation.<sup>4</sup> To overcome the above-mentioned obstacles rooted in the existing Si-based electronic devices, new problem-solving strategies beyond CMOS or even beyond von

AIP Advances **11**, 015045 (2021); doi: 10.1063/5.0030016 © Author(s) 2021 Neumann are urgently needed and have aroused extensive research interests.  $^{\rm 5,6}$

One promising strategy is to introduce the emerging nonvolatile memories such as magnetoresistive memory,<sup>7–12</sup> resistive memory,<sup>13–16</sup> and phase-change memory<sup>17</sup> into logic circuits. Fortunately, due to their nonvolatile feature, these memories can eradicate the static power dissipation. More importantly, the exploration of their logic functions will lead to the unity of logic and memory units, hence thoroughly breaking the von Neumann bottleneck. In particular, the magnetic tunnel junction based on spin transfer torque (called the STT-MTJ) combines the advantages of nonvolatility, CMOS compatibility, and unlimited endurance,<sup>18</sup> showing great potential to construct a "stateful" logic circuit where intrinsic logic-in-memory cells both perform logic operations and store logic values.<sup>6</sup> Recently, a reprogrammable logic gate consisting of three input STT-MTJs and one output STT-MTJ was designed to realize the basic Boolean logic functions AND, OR, NAND, NOR, and the Majority operation.<sup>9,10,19</sup>

However, despite the reprogrammable gates and implication gates being good examples for the realization of stateful logic, there are still some shortcomings that need to be addressed. In the aspect of device performance, the STT-MTJ suffers from serious failure and reliability issues due to the high writing current densities as well as erroneous writing by the read current.<sup>20</sup> Furthermore, both the single implication gate and the single reprogrammable gate can only implement just one or a limited number of logic operations, indicating more steps and complex combinations are needed to complement the other basic Boolean logic functions. Therefore, it is extremely attractive to explore a better alternative to the STT-MTJ and to finally realize as many Boolean logic functions as possible in such a single device.

Spin–orbit torque (SOT) originating from the spin Hall effect and Rashba–Edelstein effect provides another method to realize magnetization switching<sup>21–23</sup> and high-speed domain wall motion<sup>24,25</sup> by an in-plane current injection. Moreover, the critical current of the SOT-induced switching can be modulated with a bias voltage due to the voltage-controlled magnetic anisotropy (VCMA) effect,<sup>26,27</sup> exhibiting great potential in the application of MTJ-based logic devices.

In this work, a design based on the SOT mechanism was experimentally demonstrated to realize all 16 Boolean logic functions in a simple Ta/CoFeB/MgO trilayer with perpendicular magnetic anisotropy (PMA). The key idea is to combine different logic inputs to tune the magnetization state and to measure the anomalous Hall resistance as the logic output. Furthermore, by utilizing the tunnel magnetoresistance (TMR) value as the logic output, this method is applicable to the emerging perpendicular SOT-MTJ, a novel three-terminal device with high reliability, symmetric switching, and scalable energy consumption compared to the conventional STT-MTJ. More importantly, we also conceive that by combing the voltage-controlled magnetic anisotropy (VCMA) effect, the modified method (using current injection and bias voltage as logic inputs) can realize all 16 Boolean logic functions in the SOT-MTJ.

The multilayers with a core structure of Ta (3)/Co<sub>40</sub>Fe<sub>40</sub>B<sub>20</sub> (1.1)/MgO (2)/Ta (3) (in nm) were deposited on thermally

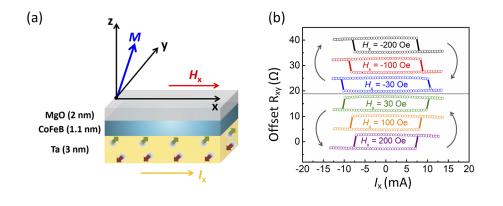

oxidized Si (001) substrates by a magnetron sputtering system at room temperature. The films were patterned into  $15-\mu$ m-wide Hall bars for transport measurements using photolithography and Ar-ion etching. The devices exhibit PMA after an annealing process at above 300 °C, which can be proved by the anomalous Hall signal with an out-of-plane magnetic field (Fig. S1, supplementary material). Figure 1(a) shows SOT-induced magnetization switching, with current injection  $(I_x)$  and magnetic field  $(H_x)$  both along the x-axis. Opposite switching can be clearly observed when  $H_x$  is reversed, suggesting similar features to the previous studies on perpendicularly magnetized heavy metal/ferromagnet heterostructures.<sup>21,28</sup> Figure 1(b) presents current-induced switching loops under different  $H_x$ , indicating that the critical switching current is positively correlated with  $H_x$ , which can be explained by the Marco model.<sup>29</sup> Moreover, programmable logic devices based on the SOT mechanism can be designed according to this relationship.

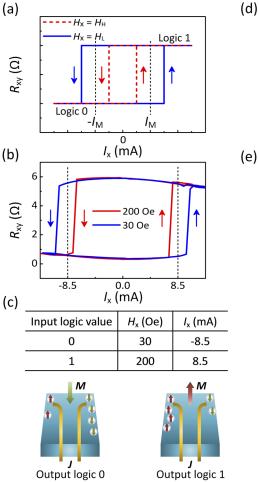

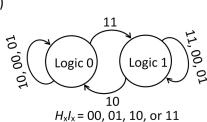

Figure 2(a) shows two schematic current-induced switching loops under different external fields in consideration of a single domain switching paradigm. The critical switching currents can be distinguished in the high external field  $(H_{\rm H})$  and low external field  $(H_{\rm L})$  configurations. Hence, a median value of two critical switching currents is defined as  $|I_{\rm M}|$ . Similar to the schematic curves, distinctly different switching loops corresponding to different external fields can be observed in the experimental measurements, as shown in Fig. 2(b). Here,  $H_{\rm H}$  and  $H_{\rm L}$  are 200 Oe and 30 Oe, respectively, and the value of  $|I_{\rm M}|$  is 8.5 mA. The external field  $H_{\rm x}$  and injected current  $I_x$  are used as two input variables to perform logic operations. For example,  $H_x$  is 30 Oe or 200 Oe for input 0 or 1, respectively, and  $I_x$  is set to -8.5 mA or +8.5 mA for input 0 or 1, as listed in the table in Fig. 2(c). The measured Hall resistance functions as the logic output, which can be identified as the spin-up state (logic "1") and the spin-down state (logic "0"), as shown in Fig. 2(c). Figure 2(d) suggests the logic output transformation corresponding to different logic inputs (external field/current,  $H_xI_x$ ). It can be seen from the diagram that for the  $H_xI_x$  = "11" configuration ( $H_x$  = 200 Oe and  $I_x = +8.5$  mA), the logic output is 1 (spin-up state), regardless of the initial magnetization state. Similarly, the  $H_xI_x$  = "10" configuration leads to the logic output 0, and SOT-induced switching will not take place with the logic input  $H_x I_x = "00"$  or "01" configuration. Based on these working principles, all 16 Boolean logic operations can be performed, and the detailed operations are listed in Fig. 2(e).

**FIG. 1.** (a) Illustration of a Ta/CoFeB/MgO Hall bar device.  $H_x$  and  $I_x$  refer to inplane field and current injection along the x axis, respectively. (b) Current switching loops under different  $H_x$  (the arrows shown in the figure indicate the switching) polarities of the SOT-induced switching).

| (e) |           |                |                       |                |                       |                |                |  |

|-----|-----------|----------------|-----------------------|----------------|-----------------------|----------------|----------------|--|

|     | Logic     | W1             |                       | W2             |                       | W3             |                |  |

|     | operation | H <sub>x</sub> | <i>I</i> <sub>x</sub> | H <sub>x</sub> | <i>I</i> <sub>x</sub> | H <sub>x</sub> | I <sub>x</sub> |  |

|     | True      | 1              | 1                     | -              | -                     | -              | -              |  |

|     | False     | 1              | 0                     | -              | -                     | -              | -              |  |

|     | p         | 1              | р                     | -              | -                     | -              | -              |  |

|     | q         | 1              | q                     | -              | -                     | -              | -              |  |

|     | NOT p     | 1              | ¬р                    | -              | -                     | -              | -              |  |

|     | NOT q     | 1              | ¬q                    | -              | -                     | -              | -              |  |

|     | p AND q   | 1              | 0                     | p              | q                     | -              | -              |  |

|     | p NAND q  | 1              | 1                     | p              | ¬q                    | -              | -              |  |

|     | p OR q    | 1              | 1                     | <i>¬p</i>      | q                     | -              | -              |  |

|     | p NOR q   | 1              | 0                     | <i>¬p</i>      | $\neg q$              | -              | -              |  |

|     | p IMP q   | 1              | 1                     | p              | q                     | -              | -              |  |

|     | p NIMP q  | 1              | 0                     | p              | ¬q                    | -              | -              |  |

|     | p RIMP q  | 1              | 1                     | <i>¬p</i>      | ¬q                    | -              | -              |  |

|     | p RNIMP q | 1              | 0                     | -p             | q                     | -              | -              |  |

|     | p XOR q   | 1              | 0                     | <i>¬p</i>      | q                     | p              | ¬q             |  |

|     | p XNOR q  | 1              | 0                     | p              | q                     | <i>-</i> p     | ¬q             |  |

|     |           |                |                       |                |                       |                |                |  |

FIG. 2. (a) Schematic switching loops under high external field  $(H_{\rm H})$  and low external field  $(H_{\rm L})$ ; the median value of two critical switching currents is defined as  $|I_{\rm M}|$ . (b) Corresponding experimental switching loops under 200 Oe (H<sub>H</sub>) and 30 Oe ( $H_L$ ), where  $|I_M|$  is 8.5 mA. (c) The correspondence between input logic values and  $H_x$  as well as  $I_x$ . The illustration suggests the output logic values corresponding to magnetization states. (d) Transition of the output logic states by  $H_x I_x$  combined operations. (e) Detailed operation methods of all 16 Boolean logic functions (W1, W2, and W3 stand for a write sequence).

Therefore, "*p*" and "*q*" are the two input logic variables, "-" means no operation, and " $\neg$ " represents the negation operation, i.e.,  $\neg 0 = 1$  and  $\neg 1 = 0$ .

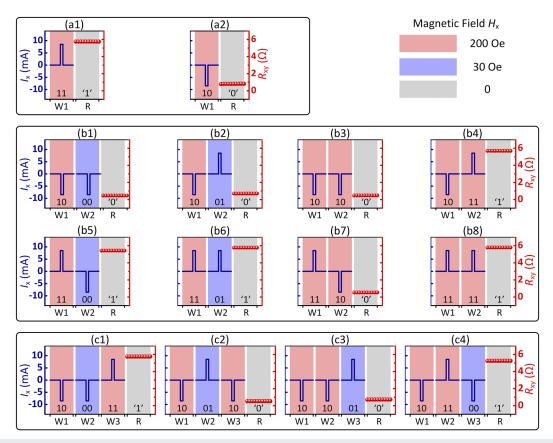

Figure 3 shows the experimental results of Boolean logic functions based on the SOT-induced switching. Combining with a truth table of all 16 Boolean logic gates (shown in supplementary material), the feasibility of complementary logic operation in a single device with programmability and non-volatility can be demonstrated. For example, a TRUE gate can be performed in one step with the logic operation "11" ( $H_x = 200$  Oe and  $I_x = +8.5$  mA), regardless of the value of inputs *p* and *q*. For this configuration, the final magnetization is in the spin-up state, outputting a logic value 1, as shown in Fig. 3(a1). For an AND gate, if the input p = q = 0, a logic operation  $H_x I_x =$  "10" ( $H_x = 200$  Oe and  $I_x = -8.5$  mA) is needed as an initialization step. Then, the writing operation "00" is performed by  $H_x = 30$  Oe and  $I_x = -8.5$  mA. In this case, the final magnetization state is "spin-down," outputting a logic value 0, as shown in Fig. 3(b1). For the configurations with other "p q" values, "01," "10," and "11," the logic function can be realized by writing "p q" after an initialization step with "10," outputting the corresponding results finally, as shown in Figs. 3(b2)-3(b4). For an OR gate, the logic input  $I_xH_x = "11"$  ( $H_x = 200$  Oe,  $I_x = +8.5$  mA) is initially operated if the input p = 1 and q = 0. Then, the write operation " $\neg p q$ " ("00,"  $H_x = 30$  Oe, and  $I_x = -8.5$  mA) is performed as the second step, resulting in the spin-up state (output 0), as shown in Fig. 3(b5). For configurations with other "p q" values, "11," "00," and "01," the logic operations can be completed by writing " $\neg p q$ " after an initialization step with "11," and the corresponding experimental results are shown in Figs. 3(b6)–3(b8).

Moreover, an XOR gate can be realized in a process with three steps. If the logic input p = 0 and q = 1, the write operation  $H_x I_x$  = "10" ( $H_x = 200$  Oe and  $I_x = -8.5$  mA) is performed at first. The second step is to input " $\neg p q$ " ("11,"  $H_x = 200$  Oe, and  $I_x = +8.5$  mA). Write operation " $p \neg q$ " ("00,"  $H_x = 30$  Oe, and  $I_x = -8.5$  mA) is performed at last. After the three-step operations, the final magnetization state is spin-up, outputting a logic value 1, as shown in Fig. 3(c4). As for the other "p q" values of "10," "11," and "00," the initial operation is to input "10" and then input " $\neg p q$ " as follows. The third step is to perform a logic operation " $p \neg q$ " and read the corresponding output values finally. The relevant experimental results are shown in Figs. 3(c1)-3(c3). In addition, the operations of other logic gates not mentioned here are

FIG. 3. Experimental results of all 16 Boolean logic functions based on the SOT switching mechanism. (a)–(c) represent the realization of logic functions by using one, two, and three write cycles, respectively.

summarized in the truth table (Fig. S2, supplementary material). It clearly indicates that these experimental results demonstrate the feasibility to successfully realize all 16 Boolean logic operations in the Ta/CoFeB/MgO device. It means that the SOT-based logic operations can be introduced into the device design, which is expected to realize the combination of non-volatile memory and computing unit in an integrated circuit, breaking the von Neumann bottleneck in the future.

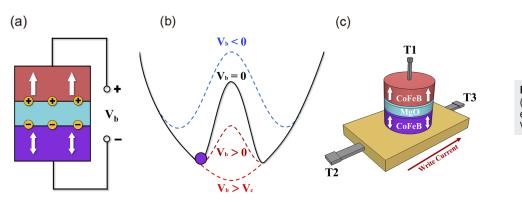

Furthermore, the external field can be replaced by bias voltage as a logic input based on the VCMA effect.<sup>30,31</sup> As shown in Fig. 4(a), charge accumulation will take place at the ferromagnetic metal/oxide interface in the MTJ structure with a bias voltage (V<sub>b</sub>) applied. The energy barrier of magnetization switching is thus modulated due to the change in the relative occupancy of the 3*d*-orbitals.<sup>32</sup> Figure 4(b) shows the specific influence of the bias voltage on the energy barrier of magnetization switching in the free layer, suggesting a lower barrier corresponding to a positive bias voltage and a higher barrier corresponding to a negative bias voltage. The voltage required to completely eliminate the barrier is defined as V<sub>c</sub>. The voltage-driven switching induced by SOT can be realized by precisely controlling the duration of the bias voltage when  $0 < V_b < V_c$ .<sup>32,33</sup> Based on this feature, a VCMA-assisted SOT MTJ device was designed, as shown in Fig. 4(c). A low energy barrier is achieved with a bias voltage applied between terminals T1 and T3, and the SOT originated from the heavy metal layer is induced by an injected current between T2 and T3 that results in a current-induced switching. This procession can be described by the Landau–Lifshitz–Gilbert (LLG) equation,<sup>34</sup>

$$\frac{d\overline{M}}{dt} = -\gamma \vec{M} \times \vec{H}_{eff} + \alpha \vec{M} \times \frac{d\overline{M}}{dt} + \vec{\Gamma}, \qquad (1)$$

where *M* is the magnetization vector,  $\gamma$  is the gyromagnetic ratio, and  $\alpha$  is the Gilbert damping coefficient. The effective magnetic field  $H_{\text{eff}} = H_{\text{ext}} + H_{\text{d}} + H_{\text{ani}}$  is the sum of the external field ( $H_{\text{ext}}$ ), the demagnetizing field ( $H_{\text{d}}$ ), and the anisotropy field ( $H_{\text{ani}}$ ). Taking into account the VCMA effect,  $H_{\text{ani}}$  can be expressed in the form<sup>33</sup>

$$\vec{H}_{ani(V_b)} = \left(\frac{2K_{i(0)}t_{ox} - 2\xi V_b}{M_s t_f t_{ox}}\right) \vec{M},\tag{2}$$

where  $K_{i(0)}$  is the interfacial anisotropy energy without bias voltage applied,  $t_{ox}$  and  $t_f$  are the thickness of the barrier and the free layer, respectively,  $\xi$  is the VCMA coefficient, and  $M_s$  is the saturation magnetization of the free layer. The additional SOT item in

FIG. 4. Illustrations of (a) MTJ structure, (b) impact of different voltages on the energy barrier of an MTJ, and (c) the VCMA-assisted SOT MTJ device.

the LLG equation can be described as

$$\vec{\Gamma} = -\frac{\gamma \hbar \theta_{\rm SHE} J}{2 e t_{\rm f} M_{\rm s}} \vec{M} \times \left( \vec{M} \times \vec{\sigma} \right), \tag{3}$$

where  $\theta_{\text{SHE}}$  is the spin Hall angle and  $\vec{\sigma}$  is the spin polarization vector. Hence, the dynamic evolution of the magnetization in the free layer can be characterized according to Eqs. (1) and (3). Based on this, Verilog-A language was applied to build electrical models for a VCMA-assisted SOT MTJ device to perform numerical simulations

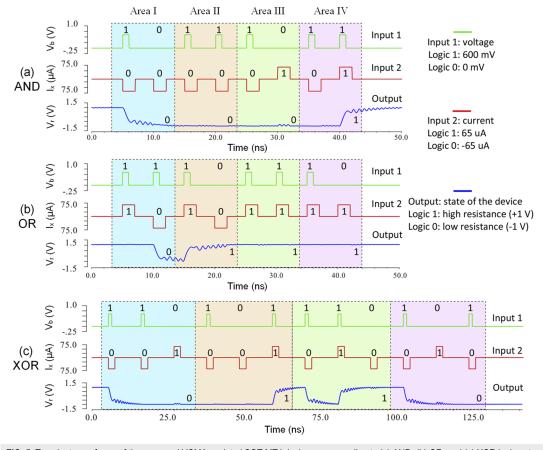

with a 40-nm CMOS kit.<sup>33</sup> The detailed parameters for the model can be found in Table S3 listed in the supplementary material. The simulation results suggest that all 16 Boolean logic functions can be realized based on the VCMA and SOT effects. Figure 5 shows the transient waveforms of the proposed VCMA-assisted SOT MTJ device corresponding to AND, OR, and XOR logic gates.

Bias voltage V<sub>b</sub> and injected current  $I_x$  are used as two input variables to perform logic operations. V<sub>b</sub> is set as 0 mV or 600 mV for input 0 or 1, respectively, and  $I_x$  is set to -65  $\mu A$  or +65  $\mu A$  for input 0 or 1, respectively. The application of bias

FIG. 5. Transient waveforms of the proposed VCMA-assisted SOT MTJ device corresponding to (a) AND, (b) OR, and (c) XOR logic gates.

voltage can lead to a lower energy barrier, and the SOT is generated by the injected current, resulting in a switching of the magnetization state of the free layer in the device. The logic output is defined based on the tunneling magnetoresistance (TMR) corresponding to the anti-parallel state (high resistance, +1 V, logic 1) or parallel state (low resistance, -1 V, logic 0) of the two ferromagnetic layers. The transient waveforms of each logic operation shown in Fig. 5 are divided into four color areas (areas I-IV), representing the operation process when the initial logic input "p q" = "00," "10," "01," and "11," respectively. For an AND gate shown in Fig. 5(a), if the inputs p = q = 0 (area I), the initialization step is to perform a logic operation "10," setting the bias voltage to 600 mV (1 ns) with a pulsed injected current of  $-65 \ \mu A$ (2 ns). Then, the logic operation "00" is performed by  $I_x = -65 \ \mu A$ without bias voltage applied. The device is in the low-resistance state finally in this case, outputting a logic value 0. For the configurations with other "p q" values, "10" (area II), "01" (area III), and "11" (area IV), the logic operation can be completed by writing "p q" after an initialization step with "10" and outputting the corresponding results. For an OR gate shown in Fig. 5(b), if the inputs p = 1 and q = 0 (area II), a write operation "11" (V<sub>b</sub> = 600 mV and  $I_x = +65 \ \mu A$ ) is performed at first. Then, the operation is completed by a write operation " $\neg p q$ " ("00," V<sub>b</sub> = 0 mV, and  $I_x = -65 \mu A$ ) that results in a high-resistance state (1 V, output 1). For configurations with other "p q" values, "00" (area I), "01" (area III), and "11" (Area IV), the logic operation can be completed by writing " $\neg p q$ " after an initialization step with "11," similar to the discussion above. Figure 5(c) shows the realization of an XOR gate with three steps. If the logic input p = 0 and q = 1 (area III), the write operation "10"  $(V_b = 600 \text{ mV} \text{ and } I_x = -65 \ \mu A)$  is performed at first, leading to the low-resistance state. The second step is to input " $\neg p q$ " ("11," V<sub>b</sub> = 600 mV, and  $I_x$  = +65  $\mu$ A), and write operation " $p \neg q$ " ("00," V<sub>b</sub> = 0 mV, and  $I_x = -65 \,\mu A$ ) is performed at last. Finally, the device is in the high-resistance state outputting a logic value 1 after the three-step operations. As for the other input values of "p q," "00" (area I), "10" (area II), and "11" (Area IV), the logic function can be performed with three operations of input "10," " $\neg p q$ ," and " $p \neg q$ ," reading the corresponding logic output value finally. Based on this, a VCMA-SOT assisted MTJ device with three terminals is designed, and the feasibility of realizing all 16 Boolean logic functions in a single unit is demonstrated. The simulation results suggest that the operation with a single step only needs 2.26 ns, featuring an ultra-fast writing speed.

In summary, all 16 Boolean logic functions in a single Ta/CoFeB/MgO device with PMA were experimentally demonstrated based on the SOT effect by applying the external field and current injection as input variables. Furthermore, the VCMA effect was introduced to design a three-terminal MTJ device, which can implement magnetic field-independent logic operations. The approach can be improved through optimization of structure design and device fabrication, paving the way for the application of energy efficient spin-based logic, which is beyond the current von Neumann computing architecture.

### SUPPLEMENTARY MATERIAL

See the supplementary material for the anomalous Hall signal of the device, the truth table of all 16 Boolean logic functions, and the detailed parameters for the electrical model to perform numerical simulations.

#### ACKNOWLEDGMENTS

This work was supported by the National Key Research and Development Program of China (Grant No. 2019YFB2005800), by the Natural Science Foundation of China (Grant Nos. 51625101, 11874082, 51971026, 61704178, and 61974179), by the NSFC-ISF Joint Research Program (Grant No. 51961145305), by the State Key Laboratory for Advanced Metals and Materials (Grant No. 2019Z-10), and by the Beijing Natural Science Foundation Key Program (Grant Nos. Z190007 and Z190008).

#### DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon request.

#### REFERENCES

<sup>1</sup>K. L. Wang, X. Kou, P. Upadhyaya, Y. Fan, Q. Shao, G. Yu, and P. K. Amiri, Proc. IEEE **104**, 1974 (2016).

<sup>2</sup>D. S. Jeong, K. M. Kim, S. Kim, B. J. Choi, and C. S. Hwang, Adv. Electron. Mater. 2, 1600090 (2016).

<sup>3</sup>N. S. Kim, T. Austin, D. Baauw, T. Mudge, K. Flautner, J. S. Hu, M. J. Irwin, M. Kandemir, and V. Narayanan, Computer **36**, 68 (2003).

<sup>4</sup>J. Backus, Commun. ACM **21**, 613 (1978).

<sup>5</sup>T. N. Theis and P. M. Solomon, Science **327**, 1600 (2010).

<sup>6</sup>J. Borghetti, G. S. Snider, P. J. Kuekes, J. J. Yang, D. R. Stewart, and R. S. Williams, Nature **464**, 873 (2010).

<sup>7</sup>S. Matsunaga, J. Hayakawa, S. Ikeda, K. Miura, H. Hasegawa, T. Endoh, H. Ohno, and T. Hanyu, Appl. Phys. Express 1, 091301 (2008).

<sup>8</sup>W. S. Zhao, C. Chappert, V. Javerliac, and J.-P. Noziere, IEEE Trans. Magn. 45, 3784 (2009).

<sup>9</sup>A. Lyle, J. Harms, S. Patil, X. Yao, D. J. Lilja, and J.-P. Wang, Appl. Phys. Lett. **97**, 152504 (2010).

<sup>10</sup>H. Mahmoudi, T. Windbacher, V. Sverdlov, and S. Selberherr, Solid-State Electron. 84, 191 (2013).

<sup>11</sup>S. Gao, G. Yang, B. Cui, S. Wang, F. Zeng, C. Song, and F. Pan, Nanoscale 8, 12819 (2016).

<sup>12</sup>A. Ney, C. Pampuch, R. Koch, and K. H. Ploog, Nature 425, 485 (2003).

<sup>13</sup>E. Linn, R. Rosezin, S. Tappertzhofen, U. Böttger, and R. Waser, Nanotechnology **23**, 305205 (2012).

<sup>14</sup>Y. Zhou, Y. Li, L. Xu, S. Zhong, H. Sun, and X. Miao, Appl. Phys. Lett. 106, 233502 (2015).

<sup>15</sup>A. Siemon, T. Breuer, N. Aslam, S. Ferch, W. Kim, J. van den Hurk, V. Rana, S. Hoffmann-Eifert, R. Waser, S. Menzel, and E. Linn, Adv. Funct. Mater. 25, 6414 (2015).

<sup>16</sup>T. You, Y. Shuai, W. Luo, N. Du, D. Bürger, I. Skorupa, R. Hübner, S. Henker, C. Mayr, R. Schüffny, T. Mikolajick, O. G. Schmidt, and H. Schmidt, Adv. Funct. Mater. 24, 3357 (2014).

<sup>17</sup>C. D. Wright, P. Hosseini, and J. A. V. Diosdado, Adv. Funct. Mater. 23, 2248 (2013).

<sup>18</sup>X. Fong, Y. Kim, R. Venkatesan, S. H. Choday, A. Raghunathan, and K. Roy, Proc. IEEE **104**, 1449 (2016).

<sup>19</sup>X. F. Yao, J. Harms, A. Lyle, F. Ebrahimi, Y. S. Zhang, and J.-P. Wang, IEEE Trans.Nanotechnol. **11**, 120 (2011).

<sup>20</sup>W. S. Zhao, Y. Zhang, T. Devolder, J. O. Klein, D. Ravelosona, C. Chappert, and P. Mazoyer, Microelectron. Reliab. **52**, 1848 (2012).

<sup>21</sup> I. M. Miron, K. Garello, G. Gaudin, P.-J. Zermatten, M. V. Costache, S. Auffret, S. Bandiera, B. Rodmacq, A. Schuhl, and P. Gambardella, Nature **476**, 189 (2011).

<sup>22</sup>L. Liu, C.-F. Pai, Y. Li, H. W. Tseng, D. C. Ralph, and R. A. Buhrman, Science 336, 555 (2012).

<sup>23</sup>L. Q. Liu, O. Lee, T. Gudmundsen, D. Ralph, and R. Buhrman, Phys. Rev. Lett. 109, 096602 (2012).

<sup>24</sup>K.-S. Ryu, L. Thomas, S.-H. Yang, and S. Parkin, Nat. Nanotechnol. 8, 527 (2013).

<sup>25</sup>I. M. Miron, T. Moore, H. Szambolics, L. D. Buda-Prejbeanu, S. Auffret, B. Rodmacq, S. Pizzini, J. Vogel, M. Bonfim, A. Schuhl, and G. Gaudin, Nat. Mater. 10, 419 (2011).

<sup>26</sup>W.-G. Wang, M. Li, S. Hageman, and C. L. Chien, Nat. Mater. 11, 64 (2012).

<sup>27</sup>T. Maruyama, Y. Shiota, T. Nozaki, K. Ohta, N. Toda, M. Mizuguchi, A. A. Tulapurkar, T. Shinjo, M. Shiraishi, S. Mizukami, Y. Ando, and Y. Suzuki, Nat. Nanotechnol. 4, 158 (2009).

<sup>28</sup>X. Wang, C. Wan, W. Kong, X. Zhang, Y. Xing, C. Fang, B. Tao, W. Yang, L. Huang, H. Wu, M. Irfan, and X. Han, Adv. Mater. **30**, 1801318 (2018).

<sup>29</sup>C. Wan, X. Zhang, Z. Yuan, C. Fang, W. Kong, Q. Zhang, H. Wu, U. Khan, and X. Han, Adv. Electron. Mater. 3, 1600282 (2017).

<sup>30</sup>C. Song, B. Cui, F. Li, X. J. Zhou, and F. Pan, Prog. Mater. Sci. 87, 33 (2017).

<sup>31</sup> F. Matsukura, Y. Tokura, and H. Ohno, Nat. Nanotechnol. 10, 209 (2015).

<sup>32</sup> M. K. Niranjan, C.-G. Duan, S. S. Jaswal, and E. Y. Tsymbal, Appl. Phys. Lett. 96, 222504 (2010).

<sup>33</sup>W. Kang, Y. Ran, W. Lv, Y. Zhang, and W. Zhao, IEEE Magn. Lett. 7, 1 (2016).

<sup>34</sup>D. V. Berkov and J. Miltat, J. Magn. Magn. Mater. **320**, 1238 (2008).