#

# Introduction of Interfacial Charges to Black Phosphorus for a Family of Planar Devices

Guocai Wang,<sup>†,‡,§</sup> Lihong Bao,<sup>†,‡,§</sup> Tengfei Pei,<sup>†,‡,§</sup> Ruisong Ma,<sup>†,‡,§</sup> Yu-Yang Zhang,<sup>||,†</sup> Liling Sun,<sup>†</sup> Guangyu Zhang,<sup>†,‡,§</sup> Haifang Yang,<sup>†</sup> Junjie Li,<sup>†</sup> Changzhi Gu,<sup>†</sup> Shixuan Du,<sup>†,‡,§</sup> Sokrates T. Pantelides,<sup>\*,||,⊥,‡</sup> Ronald D. Schrimpf,<sup>⊥</sup> and Hong-jun Gao<sup>\*,†,‡,§</sup>

<sup>†</sup>Institute of Physics, Chinese Academy of Sciences, P.O. Box 603, Beijing 100190, China

<sup>‡</sup>University of Chinese Academy of Sciences, Beijing 100190, China

<sup>§</sup>Beijing Key Laboratory for Nanomaterials and Nanodevices, Beijing 100190, China

<sup>II</sup>Department of Physics and Astronomy and <sup>⊥</sup>Institute for Space and Defense Electronics, Electrical Engineering and Computer Science Department, Vanderbilt University, Nashville, Tennessee 37235, United States

**(5)** Supporting Information

**ABSTRACT:** The capabilities to tune the conduction properties of materials by doping or electric fields are essential for the design of electronic devices. However, in two-dimensional materials substitutional doping has been achieved in only a few systems, such as Nb substitutional doping in MoS<sub>2</sub>. Surface charge transfer is still one of the popular ways to control whether the conduction is dominated by holes or electrons. Here, we demonstrate that a capping layer of cross-linked poly(methyl methacrylate) modifies the potential in a black phosphorus (BP) layer so that conduction in the absence of an external electric field is dominated by electrons, rather than holes. Using this technique to form adjoining regions dominated by hole and electron conduction, a family of

novel planar devices, such as BP-gated diodes, BP bidirectional rectifier, and BP logic inverters, can be fabricated. The devices are potentially useful for electronic applications, including rectification and switching.

**KEYWORDS**: black phosphorus, interfacial charge, field-effect transistor, p-n diode, logic inverter

T he employment of two-dimensional (2D) layered materials as building blocks for next-generation nanoelectronics, represented by graphene<sup>1</sup> and transition metal dichalchogenides (TMDCs),<sup>2</sup> provides a possible alternative route for overcoming the scaling limits in Si-based complementary metal oxide semiconductor (CMOS) devices. The 2D nature of these layered materials confines the charge carriers to an atomically thin surface,<sup>3,4</sup> allowing transistors based on them to push the scaling limits and operation speeds beyond those of Si-based transistors.<sup>5,6</sup> Despite the extremely high mobility (~20000 cm<sup>2</sup>/(V s)) and the potential to approach ballistic transport at relatively large length scale (over hundreds of micometers),<sup>7</sup> lack of a finite band gap makes graphene unsuitable for logic applications that require a large current ON/OFF ratio (>10<sup>4</sup>).<sup>8</sup> Semiconducting TMDCs, however, possess a finite and thickness-dependent band gap (ranging from  $\sim 0.5$  to  $\sim 2.2$  eV) but suffer from low carrier mobility. The emergence of few-layered black phosphorus (BP) as the channel material for FETs fills the gap between graphene and TMDCs due to its moderate bandgap (0.3 eV for bulk and 2.0 eV for monolayer) and a high hole mobility of  $\sim 1000 \text{ cm}^2/(\text{V}$ s).<sup>9–11</sup> Because of the bandgap, a current ON/OFF ratio of 5

orders of magnitude has been realized in BP FETs.<sup>9–11</sup> However, due to the Schottky barrier formation between the metal contact electrodes and BP,<sup>9,11–14</sup> a strong asymmetry in electron and hole transport in BP FETs has been observed.<sup>15–18</sup> The hole mobility and the current on/off ratio in FETs based on hole conduction are several orders of magnitude higher than the electron mobility and the on/off ratio of FETs based on electron conduction, resulting in a great challenge in realization of complementary devices in a single BP flake. Until recently, electron doping and complementary device based on a single BP flake has been achieved.<sup>19</sup>

In conventional semiconductor devices, n-type or p-type behavior is obtained by substitutional doping. In 2D materials, however, due to their stable lattice structures and absence of dangling bonds, substitutional doping has been only achieved in a few systems, such as Nb substitutionally doped MoS<sub>2</sub>.<sup>20,21</sup> The conductivity type (holes vs electrons) can be modified by electrostatic modulation via an external electrical field, but the

Received:

June 30, 2016

Revised:

October 19, 2016

Published:

October 27, 2016

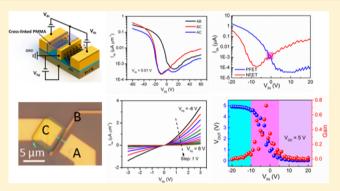

**Figure 1.** Electrical characterization of few-layer BP FETs with and without cross-linked PMMA as capping layer using Cr/Au (5/60 nm) metal stacks as contact electrodes. (a) Schematic of BP FET devices with and without cross-linked PMMA as capping layer in the same channel and their measurement setup. The brown balls and sticks stand for the BP lattice. (b) Optical image of the device. Cr/Au (5/60 nm) metal stacks are used as contract electrodes. (c) Source-drain current (logarithmic scale) of pure BP FET (black curve, AB), cross-linked PMMA-covered BP FET (red curve, BC), and BP p-n diode (blue curve, AC) as a function of gate voltage from a 10 nm-thick BP flake at room temperature with drain-source voltage of 100 mV. (d) I-V (output) characteristics of pure BP FET (AB) on the hole conduction side with negative gate bias ranging from -50 to 0 V in a step of 10 V. The observed linear behavior indicates a good contact. (e) Source-drain current of pure BP FET (AB) under large voltage bias (-3 to 0 V) with gate voltage modulation ranging from -50 to 0 V in a step of 10 V, indicating a typical P-FET behavior. (f) I-V (output) characteristics of cross-linked PMMA-capped BP FET (BC) on the electron conduction side with positive gate bias ranging from 10 to 50 V in a step of 10 V. The nonlinear behavior indicates the formation of a Schottky barrier at the contacts. (g) Source-drain current of cross-linked PMMA-capped BP FET (BC) under large voltage modulation ranging from -50 to 0 V) with gate voltage modulation a step of 10 V, indicating a typical n-FET behavior indicates the formation of a Schottky barrier at the contacts. (g) Source-drain current of cross-linked PMMA-capped BP FET (BC) under large voltage bias (-3 to 0 V) with gate voltage modulation ranging from -50 to 0 V in a step of 10 V, indicating a typical n-FET behavior, such as current saturation a punch-through state under large bias (around 3 V).

efficiency is rather limited because of the lack of good interfaces between high quality thin dielectrics and 2D materials. Another way of controlling the conductivity type is based on capping the 2D materials with a layer of polymer or absorbing specific gas molecules and adatoms,<sup>19</sup> or even dielectric engineering.<sup>5</sup> These capping layers avoid complicated device fabrication processes and produce negligible damage to the lattice structure of the underlying 2D materials. Previous work reported that capping BP layers with Al<sub>2</sub>O<sub>3</sub> or MoO<sub>3</sub> results in ambipolar transport dominated by hole conduction in the absence of an external electric field,<sup>13,18</sup> where charge transfer between the capping layer and the BP determines the conductivity type.<sup>17</sup> Ambipolar transport dominated by electrons was observed in Cs<sub>2</sub>CO<sub>3</sub>-capped BP layers.<sup>18</sup> Recently, BP FETs with Al<sub>2</sub>O<sub>3</sub> as the top gate dielectric on glass<sup>22</sup> and flexible polyimide substrates<sup>23</sup> have been reported using a dual gate configuration.

Poly(methyl methacrylate) (PMMA) is a typical positive photoresist used in electron beam lithography. Exposure with moderate-dose (typically 100–120  $\mu$ C/cm<sup>2</sup>) electron irradi-

ation causes chain scissions, while high irradiation dose exposure (typically >15 000  $\mu$ C/cm<sup>2</sup>) produces cross-linking. The cross-linked PMMA may be used as a dielectric through which an external voltage can be used to modulate the conductivity of materials through the field effect.<sup>24</sup> However, the effect of oxygen-containing molecular groups (such as CH<sub>3</sub>OOC<sup>-</sup>) generated during the cross-linking process has not been reported.<sup>25</sup> Here, we demonstrate that capping a thin BP layer with a layer of cross-linked PMMA modifies the conductivity type of the BP by a surface charge transfer process, converting a BP layer dominated by hole conduction in the absence of an external electric field to one dominated by electron conduction. Combining BP films capped by crosslinked PMMA with standard BP, a family of planar devices can be created, including BP-gated diodes (standard BP layer and cross-linked PMMA-capped BP layer in series, sharing a common back gate), and BP bidirectional rectifier (concatenating two back-to-back BP gated diodes in series in which a gatetunable potential barrier is established between the cross-linked

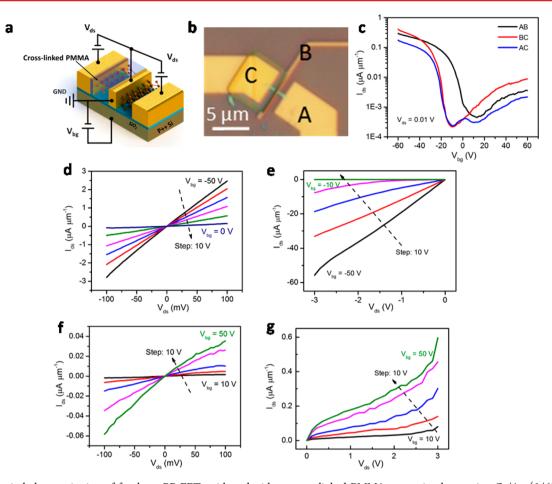

**Figure 2.** Electrical characterization of cross-linked PMMA-capped BP FET with Ni/Au (5/60 nm) metal stacks as contact electrodes. (a) Optical image (upper panel) and schematic (lower panel) of BP FET fully capped with cross-linked PMMA. (b) Source-drain current (logarithmic scale) of cross-linked PMMA-capped BP FET as a function of gate voltage with source-drain voltage of 0.1 V, showing the ambipolar transport behavior with the almost the same magnitude modulation for holes and electrons conduction. (c,e), I-V characteristics of the device on the holes conduction side at varying bias range. The near-linear behavior in (c) suggests a good contact nature, whereas in (e) a current saturation behavior is clearly observed. (d,f), I-V characteristics of the device on the electrons conduction side at varying bias range. The linear relationship between current and voltage in (d) indicates an effective reduction of the Schottky barrier at the contacts, whereas in (f) an apparent current saturation behavior is demonstrated.

PMMA-capped and uncapped regions). These devices are capable of performing either unidirectional current rectification (BP-gated diode, rectification ratio  $>10^2$ ) or bidirectional current rectification (BP bidirectional rectifier, rectification ratio  $\sim 10^2$ ), and signal inversion (BP logic inverter, gain  $\sim 0.75$ ) operations. The device performance demonstrated here suggests a promising route for developing 2D-based electronics.

BP FETs with and without Cross-Linked PMMA as Capping Layer. BP flakes with thickness of 8–10 nm are mechanically exfoliated in a glovebox onto p++ doped Si substrates with 300 nm thermal oxidized SiO<sub>2</sub> serving as the back gate dielectric. To protect the BP flakes from ambient degradation before they are exposed to atmosphere, a layer of PMMA (495, 2% in anisole) is spin coated. For contact electrode definition and a better lift-off process, an additional layer of PMMA (950, 5% in anisole) is spin coated. (Details can be found in Supporting Information Figure S1.) All electrical characterization is performed in a vacuum chamber with a vacuum level of ~10<sup>-6</sup> Torr. To investigate the effects of crosslinked PMMA capping layers on the transport properties of the underlying BP, part of the BP flake is covered, as schematically shown in Figure 1a. Figure 1b shows a typical optical image of

the device with Cr/Au (5/60 nm) contact electrodes, in which electrodes A and B coupled with a pure BP region (not capped by cross-linked PMMA) compose a pure BP FET, while electrodes B and C coupled with a cross-linked PMMA-capped BP region compose a cross-linked PMMA-capped BP FET. Figure 1c shows the transfer characteristics of a pure BP FET (black curve) and a cross-linked PMMA-capped BP FET (red curve). The pure BP FET shows ambipolar transport<sup>26</sup> dominated by hole conduction at zero gate voltage with current modulation of  $\sim 10^3$ , which is consistent with previous reports.<sup>9–13,18,27–31</sup> For  $V_{bg} < 0$ , the output characteristics of the pure BP FET with small (Figure 1d) and large (Figure 1e) source-drain bias, show a well-defined p-channel FET behavior. For  $V_{bg} > 0$ , corresponding to electron conduction (Figure 1f,g), the output characteristics of cross-linked PMMA-capped BP FET show a strong nonlinear behavior (Supporting Information Figure S3), indicating a Schottky contact.<sup>5</sup> Compared with the pure BP FET, the transfer characteristics of the cross-linked PMMA-capped BP FET show ambipolar behavior, dominated by electron conduction at zero gate voltage and characterized by a negative threshold voltage (red curve in Figure 1c), suggesting positive charges are introduced at the interface between the cross-linked PMMA and the BP surface, resulting in electrons in the BP layer as previously reported using Al<sub>2</sub>O<sub>3</sub> and Cs<sub>2</sub>CO<sub>3</sub> as the capping layer.<sup>13,17,18,32</sup> The amount of interfacial charge can be controlled by varying the electron beam dose used to irradiate the PMMA, characterized by the successive shift of the current-voltage characteristics to more negative voltages with increasing dose (Supporting Information Figure S8). Furthermore, capping with cross-linked PMMA yields enhanced electron transport behavior, including improved magnitude of current modulation on the electron conduction side of the transfer characteristics (red curve in Figure 1c) and a near-linear relationship in the output characteristics (Figure 1f,g), indicating an effective reduction of Schottky barrier height at the contact edge.<sup>17,18</sup> As for the carrier mobility, in the pure BP FET hole and electron mobilities are extracted from the transfer curve in Figure 1c as 90.7 and 1.4  $\text{cm}^2/(\text{V s})$ , respectively, whereas in the crosslinked PMMA-capped BP FET, they are 175.4 and 3.0  $\text{cm}^2/(\text{V}$ s) (Supporting Information Figure S6), respectively. The enhanced carrier mobility can be attributed to the improvement of contact features.<sup>18</sup>

Considering that Ni has higher work function (5.0 eV) than Cr (4.5 eV), it is expected that using Ni as contact electrodes will provide a better contact to regions dominated by hole conduction, based on ideal metal-semiconductor contact theory.<sup>8</sup> To further investigate the effect of the cross-linked PMMA-capping layer on the transport properties, we fabricated a BP FET fully capped with cross-linked PMMA using Ni/Au (5/60 nm) as the contact electrodes, as schematically shown in the lower panel of Figure 2a. The upper panel of Figure 2a shows an optical image of the device. Surprisingly, the transfer characteristic of the device shown in Figure 2b indicate that using Ni/Au stacks as contact electrodes favors electron transport, resulting in more symmetric ambipolar transport with almost the same current modulation for holes and electrons,  $\sim 10^2 - 10^3$ , indicating a more symmetric band alignment compared to that of Cr (Figure 1c). Previous reports suggested that for thin (<3 layer) BP flakes, metal contacts with both large (Pd, 5.2 eV) and small (Ti, 4.35 eV) work function can favor hole conduction, indicating Fermi level pinning is present at the contact interface.<sup>13</sup> For thick (>20 layers) BP flakes, metal contacts with lower work function (Ni, 5.0 eV) result in better ambipolar transport compared to that of higher work function metal (Pd, 5.2 eV), suggesting no Fermi level pinning at the contacts.<sup>12</sup> In our case, larger work function Ni contacts lead to better ampipolar transport compared to that of Cr contacts (Figure 1c), indicating a lower Schottky barrier height and better carrier injection efficiency from the Ni contact. This can be further verified by the output characteristics of the device, as shown in panels c-f in Figure 2. Under small source-drain bias (from -100 to 100 mV), both for electron ( $V_{\rm bg}$  > 0, Figure 2d) and hole conduction ( $V_{\rm bg}$  < 0, Figure 2c), the current shows a strong linear relationship, indicating a smaller Schottky barrier height compared to that of Cr (Supporting Information Figure S4). Under large sourcedrain bias, for the parts of the current-voltage relationship dominated by holes (Figure 2e) and electrons (Figure 2f), the device shows pronounced current saturation, suggesting the successful realization of both BP p-type FETs (PFET) and ntype FETs (NFET). The availability of BP PFETs and NFETs inspires us to construct BP complementary circuits.

*BP-Gated Diodes.* On the basis of the electron-dominated conductivity of cross-linked PMMA-capped BP regions and the

hole-dominated conductivity of pure BP regions, we can construct a BP diode by combining a pure BP FET and crosslinked PMMA-capped BP FET in series, as schematically shown in Figure 1a. Note that this is not a conventional PN diode because of the metal contact separating the two regions, although it does exhibit some analogous behavior. Figure 3a

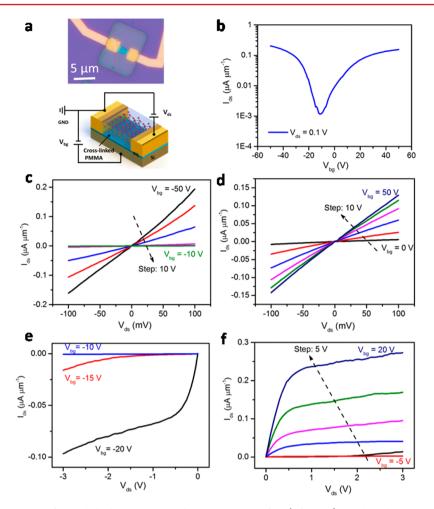

**Figure 3.** Electrical characterization of BP p–n diodes with Cr/Au (5/ 60 nm) metal stacks as contact electrodes. (a) Linear plot of I-V (output) characteristics of BP diode (shown in Figure 1b) under gate voltage modulation ranging from -5 to 5 V in a step of 2 V. The typical rectification behavior reveals the formation of BP diode, and reverse bias punch-through under large gate voltage (-5 V, black curve). (b) Logarithmic plot of the current output characteristics, suggesting a gate-tunable rectification behavior with a highest rectification ratio of ~100 under large back gate voltage (3 V).

shows the linear plot of output characteristics of a representative device under different gate bias (ranging from -5 to 5 V in a step of 2 V). A logarithmic plot is shown in Figure 3b. From the output characteristics, we can see that at  $V_{\rm bg}$  = -5 and -3 V, there is little rectification because both regions are dominated by hole conduction at this gate bias. For the other gate voltages, the device shows good rectification behavior with gate tunable rectification ratios (Supporting Information Figure S7). The rectification is produced by the asymmetry in the hole and electron conduction branches, shown in Figure 1c. Because of the middle contact, the current-voltage relationship is not described by a Boltzmann relationship (either the ideality factor is far larger than 2 or the fit is poor  $(r^2 < 70\%)$ ), as shown in Supporting Information Figure S7. The transfer curve (blue curve in Figure 1c) further demonstrates the gate tuning capability of the BP diode. The current on/off ratio is in the range of  $10^3-10^4$ , satisfying the requirements of logic operations. The two valleys (conduction minima) in the transfer curve (blue curve in Figure 1c) correspond to the depleted states of the cross-linked PMMAcapped BP and pure BP, respectively. As previously reported for

**Figure 4.** Electrical characterization of BP p–n diodes with Ni/Au (5/60 nm) metal stacks as contact electrodes. (a) Optical image of BP p–n diode fabricated by partially capped the BP conduction with cross-linked PMMA. Contact electrodes are made of Ni/Au (5/60 nm) stacks. (b) The forward diode current as a function of back gate voltages at constant source-drain bias of 0.1 V. (c) Current versus bias voltage under gate voltage modulation in the range of -6 to 6 V with a step of 1 V. (d) Logarithmic plot of the current–voltage characteristics in (c). Bipolar switching behavior of the device can be observed in both reverse (pink background) and forward bias (blue background) regimes, showing both reverse bias and forward bias have a high current on/off ratio (close to  $10^5$  at forward bias and gate voltage of 6 V). The lowest current can reach  $10^{-6} \,\mu A \,\mu m^{-1}$ , showing a completely "off" state. (e) Schematic diagram of the energy band at the points labeled as "1", "2", "3", "4", and "5" in transfer curve of the device shown in (b)."1" and "5" represent the holes conduction and electron conductions, respectively. "2"and "4" stand for flat-band for holes and electrons conduction, respectively, and "3" stands for the potential barrier that is built-up between the capped region and uncapped region.

a carbon nanotube- $MOS_2$  heterojunction p-n diode,<sup>33</sup> the transfer curve of the BP diode can be qualitatively viewed as a superposition of the transfer curves of the p-type pure BP FET (black curve in Figure 1c) and the n-type cross-linked PMMA-capped BP FET (blue curve in Figure 1c), except that the net current flowing through the diode is smaller than that of pure BP FET and capped BP FET on the electron conduction side. As discussed above, Ni has a better band alignment than Cr when in contact with BP (Figure 2).

To examine contact effects, we fabricated BP diodes using Ni/Au (5/60 nm) as the contact electrode and to avoid the formation of an additional Schottky barrier the middle electrode was removed. A representative optical image of such a device is shown in Figure 4a. Figure 4c shows the output characteristics of the device under gate bias modulation ranging from -6 to 6 V with a step of 1 V and Figure 4d is a logarithmic plot. Current rectification behavior also is observed for this device. Compared to devices using Cr/Au as the contact metal, the reverse current shows a clear saturation behavior at large reverse bias, confirming the improvement of contact features. At gate biases ranging from -6 to -3 V, the device does not exhibit significant rectification, while at other gate biases, the device shows a typical diode behavior with a gate-tunable rectification ratio ranging from  $\sim 2$  to  $\sim 70$  (Supporting

Information Figure S13). Although the rectification ratio is relatively low compared to other 2D material-based diodes,<sup>27,33-39</sup> our device shows a pronounced bipolar current switching behavior. Under reverse bias (light magenta shaded region in Figure 4d), the device shows an apparent current saturation behavior at large reverse bias voltages, and both the on-state current,  $I_{on}$ , and the off-state current,  $I_{off}$ , determined by the height of potential barrier can be modulated by  $V_{bg}$ yielding an  $I_{on}/I_{off}$  ratio of ~10<sup>3</sup>-10<sup>4</sup>. Under forward bias (light cyan-shaded region in Figure 4d), the current does not saturate and shows switching operation with an  $I_{\rm on}/I_{\rm off}$  ratio of  $10^4 - 10^5$ at  $V_{ds} = 3$  V (Supporting Information Figure S13). Figure 4b shows the current modulation of the diode for  $V_{\rm bg}$  ranging from -60 to 60 V at a forward bias of 0.1 V. Under gate bias modulation, the diode transitions from a p-p junction at  $V_{bg}$  = -50 V (labeled as "1") to an n-n junction at  $V_{bg} = 50$  V (labeled as "5"), during which two valleys appearing at  $V_{bg} = -2$ and 3.5 V (labeled as "2" and "4", respectively) reveal the depletion state for the capped BP (p-i junction) and pure BP (n–i junction), respectively. The peak at  $V_{bg} = -0.4$  V (labeled as "3") indicates the formation of a potential barrier between the capped and uncapped regions. Band diagrams of these featured points are schematically shown in Figure 4e, indicating the progressive tuning of the potential barrier.

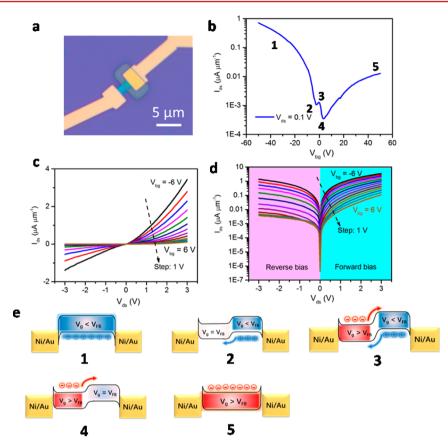

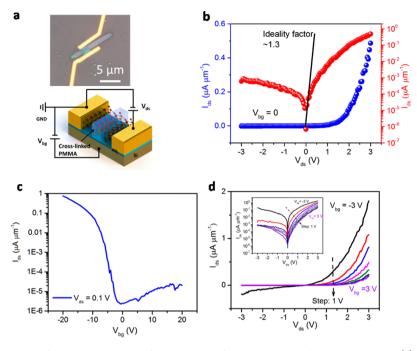

**Figure 5.** Electrical characterization of BP bidirectional rectifier composed of two BP diodes in back-to back series. (a) Optical image (upper panel) and schematic diagram (lower panel) of the device composed of two identical BP diodes in back-to-back series. Ni/Au (5/60 nm) stacks are used as contact electrodes and for efficient gate modulation, SiO<sub>2</sub> layer of 100 nm is used as gate dielectric. (b) Source-drain current as a function of both reverse and forward bias voltages at  $V_{bg} = 0$ . Blue scatters show the linear plot, while red scatters show the logarithmic plot. Fitting the logarithmic plot at small bias with Schockley's equation yields an ideality factor of ~1.3. (c) Source-drain current as a function of gate voltage bias at a constant source-drain current of 0.1 V. (d) Source-drain current versus bias voltage under gate voltage modulation ranging from -3 V to +3 V in a step of 1 V. Inset is the logarithmic plot.

BP Bidirectional Rectifier. The combination of cross-linked PMMA-capped and pure BP FETs in series yields a back-gated BP diode. What if we combine two gated BP diodes back-toback in series? This configuration is schematically shown in the lower panel of Figure 5a and the upper panel is an optical image of a representative device. We can realize it by placing a strip of cross-linked PMMA at the central part of a normal pure BP FET. Figure 5b shows the current as a function of bias voltage for the device at  $V_{bg} = 0$ . At reverse bias and low forward bias, the current is on the order of  $10^{-11}-10^{-9}$  A, corresponding to the off state. When the forward bias reaches 1 V, the current shows a rapid, near-exponential, increase. Moreover, as the bias increases from 0 to 0.05 V, the current increases by almost 2 orders of magnitude, a hallmark of diode behavior. Fitting the data in the low bias voltage range with Schockley's equation yields an ideality factor of ~1.3. The rectification ratio is ~ $10^2$ . Because of the symmetric configuration of the device (Figure 5a), the capability of rectification should not depend on the voltage bias direction. As shown in Supporting Information Figure S15, when the bias direction is changed, the device shows almost the same rectification behavior. In this regard, this device is called BP bidirectional rectifier. If the strip of crosslinked PMMA was placed off the central part of the transport channel, an asymmetric BP bidirectional rectifier is obtained. The schematic and scanning electron microscopy (SEM) image of the device is shown in Supporting Information Figure S16a. The output characteristics of the device shown in Supporting Information Figure S16c,d clearly shows its asymmetric rectification behavior. If the contact region of the device is capped by two strips of cross-linked PMMA, respectively, similar bidirectional rectification behavior can be observed, as shown in Supporting Information Figure S17. The capped

region shows electron-dominated conduction (Figure 1d), while the bare BP at both sides shows hole-dominated conduction. Because introduction of charges by the crosslinked PMMA-capping layer at the interface creates an electrostatic potential that can be considered as an "effective top gate" and shifts the Fermi level of the BP under the capped region, a gate-tunable potential barrier<sup>24</sup> can be built up between the cross-linked PMMA-capped region and the uncapped region. When the device is biased, both majority holes and minority electrons will cross the potential barrier through diffusion once they gain enough energy ( $V_{bg} = 0, V_{ds} > 0$ , Figure 5b).<sup>24</sup> The capping layer of cross-linked PMMA, serving as an "effective" top gate, tunes the Fermi level of the capped region, while the global back gate voltage can tune the carrier density in the whole BP transport channel. Correspondingly, the height of the potential barrier can be tuned through  $V_{\rm bg}$  modulation. To enhance the back gate modulation efficiency, a 100 nm SiO<sub>2</sub> layer is used as the gate dielectric and to reduce the contact resistance, Ni/Au (5/60 nm) is used as the contact metal. Figure 5d shows the typical output characteristics of the BP bidirectional rectifier under  $V_{bg}$ modulation from -3 to 3 V and the inset shows the same data in a logarithmic plot. The rectification behavior of the device is indicated by the steep increase of the current  $(I_{ds})$ once the bias voltage  $(V_{\rm ds})$  surpasses the turn-on voltage  $V_{\rm to.}$ The turn-on voltage is defined where the current exceeds the reverse-bias saturation current.  $V_{\rm to}$  can be tuned between 0 and 0.85 V when sweeping  $V_{\rm bg}$  from -3 to 3 V. A logarithmic plot of the output curve suggests that the BP bidirectional rectifier can work in two different regimes, as shown in the inset of Figure 5d. In the first regime, the BP bidirectional rectifier behaviors like a conventional FET when it is reverse-biased,

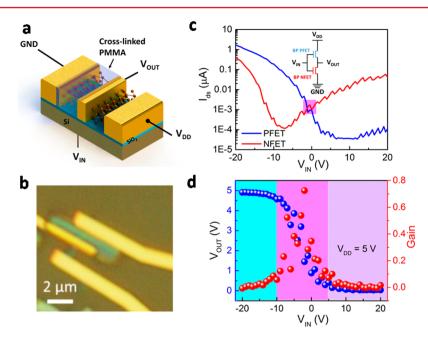

**Figure 6.** Electrical characterization of a few-layer BP logic inverter. (a) Schematic diagram of the logic inverter. (b) Optical image of the BP logic inverter. (c) Transfer characteristic of BP PFET and BP NFET realized by capping of cross-linked PMMA, showing their PFET and NFET behaviors, respectively. Inset is an equivalent circuit diagram. The enclosed pink window indicates the region where the inverter has the highest output gain. (d) The output voltage and gain as a function of input voltage, showing a highest gain of 0.75 is obtained. The cyan-, pink-, and violet-shaded areas indicate three different working regimes of the BP logic inverter.

where the current shows a tendency to saturate at large reversebias voltages. A current on/off ratio of  $10^2-10^3$  can be obtained, in which the off current is located at the greatest attainable potential barrier. In the second regime, the BP bidirectional rectifier works like a diode when it is forwardbiased. The current increases exponentially at large bias voltages and does not saturate. Near the turn-on voltage, with  $V_{bg}$  modulation the current can be varied by several orders of magnitude, indicating switching operation with high current on/off ratio. The blue curve in Figure 5d shows the switching operation of the BP bidirectional rectifier when it is in a forward-biased state, revealing a high on/off ratio of  $10^5-10^6$ . This suggests that our BP bidirectional rectifier has promising applications in digital switching devices and current rectifiers without considering the bias direction.

BP Logic Inverter. Finally we demonstrate a logic inverter based on a cross-linked PMMA-capped ambipolar BP FET and a BP ordinary FET. Figure 6a shows a 3D cartoon of the device fabricated on an individual BP flake by capping the half portion of the ordinary BP FET with cross-linked PMMA. The BP NFET function is realized in the capped region and the PFET function is realized in the uncapped region (Figure 1).  $V_{IN}$ , the input voltage, is applied to the back gate.  $V_{\rm OUT}$  is the output voltage and  $V_{\rm DD}$  is the supply voltage. Figure 6b is a photograph of the BP logic inverter based on our cross-linked PMMAcapped BP NFET and pure BP PFET. Figure 6c shows the transfer characteristics as a function of input voltage  $V_{\rm IN}$ . The capping of cross-linked PMMA induces a threshold voltage (or charge neutrality point) shift, where the capping layer works like an effective top gate and shifts the Fermi level of the capped region. This results in NFET-like operation (indicated by the negative charge neutrality point in the transfer curve shown in Figure 6c). The input voltage  $V_{IN}$  can tune the carrier density of the whole BP transport channel and combine with the cross-linked PMMA "top gate" to generate the inverted

signal,  $V_{OUT}$ . Figure 6d shows the output voltage and gain of the inverter as a function of input voltage. The output voltage shows three different regimes. In the first regime (cyan-shaded region), with the input voltage  $V_{\rm IN}$  between -20 and -10 V, the output voltage is in the "high" state with a tendency to drop with a flat slope, and correspondingly, the gain (G), defined as the slop of the output characteristics,<sup>13</sup> that is  $G = dV_{OUT}/dV_{IN}$ , gently increases. When the input voltage  $V_{\rm IN}$  is between -10and 5 V (pink-shaded region), the output voltage  $V_{\rm OUT}$  shows a transition from the "high" to "low" ( $V_{\rm OUT}$  = ~0) state with a steep slope and the gain follows a Dirac- $\delta$  function like behavior with a highest value of 0.75. An ideal logic inverter should have an infinite gain and no such transition in output voltage occurs. When the input voltage  $V_{\rm IN}$  is further increased, the output voltage  $V_{\text{OUT}}$  stays steadily at the "low output" state with a near zero value. From the transfer curves of the BP NFET and PFET (shown in Figure 6c), we can see that the transition regime of the inverter covers the steepest portion of the subthreshold region of both the BP NFET and PFET; consequently, the highest gain appears in this region, indicated by the pink shaded region in Figure 6c. One limiting factor of the low gain of the inverter is that the subthreshold slopes of the BP PFET and NFET at the crossover region (indicated by the pink box in Figure 6c) are 2.5 and 5.3 V/decade, respectively, which is much greater than the ideal slope of 60 mV/decade. The other factor limiting the gain of the inverter is the current saturation behavior in the device. As shown in Supporting Information Figure S17b, the output characteristic of PFET does not show an expected saturation behavior, which inevitably reduces the gain of the inverter. From the output curve shown in Figure S17c, the BP NFET shows a Schottky contact behavior, indicating that contact resistance is also a limiting factor. Using a thinner gate dielectric, or a high-k dielectric, like HfO<sub>2</sub>, and lower contact resistance will result in enhancement of the gain.<sup>13</sup> Another key parameter for logic inverter applications is

#### **Nano Letters**

the matching of output and input voltages. Compared to previous reports on logic inverters based on  $MoS_2$ ,<sup>27,40</sup> WSe<sub>2</sub>,<sup>41</sup> black phosphorus,<sup>19,27</sup> and so forth, our BP logic inverter shows a small mismatch of output and input voltages (Figure 6c). This mismatch probably comes from the shift of the transfer curve of PFET toward negative input voltages, which is induced by desorption of O<sub>2</sub> or H<sub>2</sub>O at the exposed BP surface when the current passes through the channel. Capping the exposed BP part with a stable and undoped layer, such as BN, will prevent the adsorption of O<sub>2</sub> and H<sub>2</sub>O on BP surface and matching output and input voltages can be obtained. Therefore, further work still needs to be done for an optimized gain and matched input and output voltages.

In summary, capping the BP FET with a layer of cross-linked PMMA introduces interfacial charges that converts the holedominated conduction to electron-dominated conduction. Combining the capped and pure BP FETs, a family of novel planar devices can be created, including BP-gated diodes, BP barristors, and BP logic inverters. These devices are potentially useful in digital electronic circuits that require current rectification, switching, and inversion. Moreover, these devices have the capability of lateral scaling due to the formation of a potential barrier in the vertical direction and provide a promising route for development of future 2D electronics.

Methods. The BP crystal was synthesized under highpressure and high-temperature conditions with red phosphorus as a starting material, as previously reported.<sup>42</sup> BP flakes with thickness of around 10 nm were mechanically exfoliated using a Scotch tape method onto p++ Si substrates with a thermal oxidized SiO<sub>2</sub> layer of 100 or 300 nm. To minimize the atmospheric exposure, the exfoliation process is performed in a glovebox. To protect the BP flakes from degrading in atmospheric conditions, after exfoliation, the substrate is spin coated with a layer of PMMA (495, 2% in anisole) before being taken out for e-beam lithography. The thickness of the BP flakes was determined by a combination of atomic force microscopy and optical contrast, also verified by Raman spectrum characterization. The devices were fabricated using a standard e-beam lithography technique, followed by thermal evaporation of Cr/Au or Ni/Au (thickness 5/60 nm) metal stacks as contact electrodes (Supporting Information Figure S1). All measurements were performed in a vacuum chamber with vacuum level better than 10<sup>-6</sup> Torr at room temperature and the electrical transport data were recorded by a Keithley 4200 SCS system and Agilent 4156 A.

#### ASSOCIATED CONTENT

#### **S** Supporting Information

The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acs.nano-lett.6b02704.

Detailed fabrication process of BP devices, Raman and AFM characterization of BP flakes, Schottky barrier reduction by capping with cross-linked PMMA in BP FETs, extraction of carrier mobility, tuning the introduced charges by varying dosage of electron beam, Raman characterization of original and cross-linked PMMA, determination of ideality factor of the BP diode based on the Schockley equation (PDF)

#### AUTHOR INFORMATION

#### **Corresponding Authors**

\*E-mail: (S.T.P.) pantelides@vanderbilt.edu.

## \*E-mail: (H.-J.G.) hjgao@iphy.ac.cn.

### **Author Contributions**

G.W. and L.B. contributed equally to this work. H.-J.G. supervised the entire project. G.C.W. and L.H.B. fabricated the devices. G.C.W., L.H.B., T.F.P., and R.S.M. performed transport measurements. L.L.S. provided the black phosphorus crystal. G.Y.Z. partially provided the measurement facility. H.F.Y., J.J.L., and C.Z.G. provided the microfabrication facilities for device fabrication. S.X.D. provided theoretical support. G.C.W., L.H.B., S.T.P., and R.D.S. analyzed the data. L.H.B. drafted the manuscript in consultation with H.-J.G., S.X.D., S.T.P, and R.D.S. All authors edited the manuscript.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

This work is supported by National "973" Projects of China (Grant 2013CBA01600), National Key Research & Development Projects of China (Grant 2016YFA0202300), National Natural Science Foundation of China (Grants 61474141, 61674170, 61335006, 61390501, 51325204, 51210003), the Chinese Academy of Sciences (CAS), and Youth Innovation Promotion Association of CAS (20150005). Y.Y.Z and S.T.P are supported in part by the Department of Energy (Grant DE-FG02-09ER46554) and acknowledge National Center for Supercomputing Applications, which is supported by the DOE Office of Science under Contract No. DE-AC02-05CH11231, and the Extreme Science and Engineering Discovery Environment (XSEDE), which is supported by National Science Foundation Grant ACI-1053575.

#### REFERENCES

(1) Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. *Science* **2004**, *306* (5696), 666–669.

- (2) Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. *Nat. Nanotechnol.* **2011**, *6* (3), 147–150.

- (3) Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Katsnelson, M. I.; Grigorieva, I. V.; Dubonos, S. V.; Firsov, A. A. *Nature* **2005**, 438 (7065), 197–200.

- (4) Zhang, Y. B.; Tan, Y. W.; Stormer, H. L.; Kim, P. Nature 2005, 438 (7065), 201–204.

- (5) Murali, R., Graphene Transistors. In *Graphene Nanoelectronics: From Materials to Circuits*; Murali, R., Ed.; Springer: New York, 2012; pp 51–93.

- (6) Wang, Q. H.; Kalantar-Zadeh, K.; Kis, A.; Coleman, J. N.; Strano, M. S. Nat. Nanotechnol. **2012**, 7 (11), 699–712.

- (7) Du, X.; Skachko, I.; Barker, A.; Andrei, E. Y. Nat. Nanotechnol. 2008, 3 (8), 491–495.

- (8) Sze, S. M.; Ng, K. K. *Physics of Semiconductor Devices*; John Wiley &Sons, Inc.: Hoboken, New Jersey, 2007.

- (9) Li, L.; Yu, Y.; Ye, G. J.; Ge, Q.; Ou, X.; Wu, H.; Feng, D.; Chen, X. H.; Zhang, Y. Nat. Nanotechnol. **2014**, 9 (5), 372–377.

- (10) Koenig, S. P.; Doganov, R. A.; Schmidt, H.; Castro Neto, A. H.; Oezyilmaz, B. *Appl. Phys. Lett.* **2014**, *104* (10), 103106.

- (11) Liu, H.; Neal, A. T.; Zhu, Z.; Luo, Z.; Xu, X.; Tomanek, D.; Ye, P. D. ACS Nano **2014**, 8 (4), 4033–4041.

- (12) Du, Y.; Liu, H.; Deng, Y.; Ye, P. D. ACS Nano 2014, 8 (10), 10035-10042.

- (13) Das, S.; Demarteau, M.; Roelofs, A. ACS Nano 2014, 8 (11), 11730–11738.

- (14) Cai, Y.; Zhang, G.; Zhang, Y.-W. Sci. Rep. 2014, 4, 6677.

(15) Das, S.; Zhang, W.; Demarteau, M.; Hoffmann, A.; Dubey, M.; Roelofs, A. Nano Lett. 2014, 14 (10), 5733-5739.

(16) Na, J.; Lee, Y. T.; Lim, J. A.; Hwang, D. K.; Kim, G.-T.; Choi, W. K.; Song, Y.-W. ACS Nano 2014, 8 (11), 11753-11762.

(17) Liu, H.; Neal, A. T.; Si, M.; Du, Y.; Ye, P. D. IEEE Electron Device Lett. 2014, 35 (7), 795-797.

(18) Xiang, D.; Han, C.; Wu, J.; Zhong, S.; Liu, Y.; Lin, J.; Zhang, X.-A.; Hu, W. P.; Oezyilmaz, B.; Castro Neto, A. H.; Wee, A. T. S.; Chen, W. Nat. Commun. 2015, 6, 6485.

(19) Koenig, S. P.; Doganov, R. A.; Seixas, L.; Carvalho, A.; Tan, J. Y.; Watanabe, K.; Taniguchi, T.; Yakovlev, N.; Castro Neto, A. H.; Özyilmaz, B. Nano Lett. 2016, 16 (4), 2145-2151.

(20) Suh, J.; Park, T.-E.; Lin, D.-Y.; Fu, D.; Park, J.; Jung, H. J.; Chen, Y.; Ko, C.; Jang, C.; Sun, Y.; Sinclair, R.; Chang, J.; Tongay, S.; Wu, J. Nano Lett. 2014, 14 (12), 6976-6982.

(21) Laskar, M. R.; Nath, D. N.; Ma, L.; Lee, E. W.; Lee, C. H.; Kent, T.; Yang, Z.; Mishra, R.; Roldan, M. A.; Idrobo, J.-C.; Pantelides, S. T.; Pennycook, S. J.; Myers, R. C.; Wu, Y.; Rajan, S. Appl. Phys. Lett. 2014, 104 (9), 092104.

(22) Kim, J. S.; Jeon, P. J.; Lee, J.; Choi, K.; Lee, H. S.; Cho, Y.; Lee, Y. T.; Hwang, D. K.; Im, S. Nano Lett. 2015, 15 (9), 5778-5783.

(23) Zhu, W.; Yogeesh, M. N.; Yang, S.; Aldave, S. H.; Kim, J.-S.; Sonde, S.; Tao, L.; Lu, N.; Akinwande, D. Nano Lett. 2015, 15 (3), 1883-1890.

(24) Huard, B.; Sulpizio, J. A.; Stander, N.; Todd, K.; Yang, B.; Goldhaber-Gordon, D. Phys. Rev. Lett. 2007, 98 (23), 236803.

(25) Lee, E. H.; Rao, G. R.; Mansur, L. K. Radiat. Phys. Chem. 1999, 55 (3), 293-305.

(26) Pfleiderer, H.; Kusian, W. Solid-State Electron. 1986, 29 (3), 317-319.

(27) Deng, Y.; Luo, Z.; Conrad, N. J.; Liu, H.; Gong, Y.; Najmaei, S.; Ajayan, P. M.; Lou, J.; Xu, X.; Ye, P. D. ACS Nano 2014, 8 (8), 8292-8299.

(28) Xia, F.; Wang, H.; Jia, Y. Nat. Commun. 2014, 5, 4458.

(29) Buscema, M.; Groenendijk, D. J.; Steele, G. A.; van der Zant, H. S. J.; Castellanos-Gomez, A. Nat. Commun. 2014, 5, 4651.

(30) Wood, J. D.; Wells, S. A.; Jariwala, D.; Chen, K.-S.; Cho, E.; Sangwan, V. K.; Liu, X.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Nano Lett. 2014, 14 (12), 6964-6970.

(31) Buscema, M.; Groenendijk, D. J.; Blanter, S. I.; Steele, G. A.; van der Zant, H. S. J.; Castellanos-Gomez, A. Nano Lett. 2014, 14 (6), 3347-3352.

(32) Haratipour, N.; Koester, S. J. IEEE Electron Device Lett. 2016, 37 (1), 103-106.

(33) Jariwala, D.; Sangwan, V. K.; Wu, C.-C.; Prabhumirashi, P. L.; Geier, M. L.; Marks, T. J.; Lauhon, L. J.; Hersam, M. C. Proc. Natl. Acad. Sci. U. S. A. 2013, 110 (45), 18076-18080.

(34) Choi, M. S.; Qu, D.; Lee, D.; Liu, X.; Watanabe, K.; Taniguchi, T.; Yoo, W. J. ACS Nano 2014, 8 (9), 9332-9340.

(35) Gong, Y.; Lin, J.; Wang, X.; Shi, G.; Lei, S.; Lin, Z.; Zou, X.; Ye,

G.; Vajtai, R.; Yakobson, B. I.; Terrones, H.; Terrones, M.; Tay, B. K.; Lou, J.; Pantelides, S. T.; Liu, Z.; Zhou, W.; Ajayan, P. M. Nat. Mater.

2014, 13 (12), 1135-1142. (36) Yu, W. J.; Li, Z.; Zhou, H.; Chen, Y.; Wang, Y.; Huang, Y.;

Duan, X. Nat. Mater. 2012, 12 (3), 246-252.

(37) Baugher, B. W. H.; Churchill, H. O. H.; Yang, Y.; Jarillo-Herrero, P. Nat. Nanotechnol. 2014, 9 (4), 262-267.

(38) Lee, C.-H.; Lee, G.-H.; van der Zande, A. M.; Chen, W.; Li, Y.; Han, M.; Cui, X.; Arefe, G.; Nuckolls, C.; Heinz, T. F.; Guo, J.; Hone, J.; Kim, P. Nat. Nanotechnol. 2014, 9 (9), 676-681.

(39) Britnell, L.; Gorbachev, R. V.; Jalil, R.; Belle, B. D.; Schedin, F.; Mishchenko, A.; Georgiou, T.; Katsnelson, M. I.; Eaves, L.; Morozov, S. V.; Peres, N. M. R.; Leist, J.; Geim, A. K.; Novoselov, K. S.; Ponomarenko, L. A. Science 2012, 335 (6071), 947-950.

(40) Su, Y.; Kshirsagar, C. U.; Robbins, M. C.; Haratipour, N.; Koester, S. J 2D Mater. 2016, 3 (1), 011006.

(41) Tosun, M.; Chuang, S.; Fang, H.; Sachid, A. B.; Hettick, M.; Lin,

Y.; Zeng, Y.; Javey, A. ACS Nano 2014, 8 (5), 4948-4953.

(42) Endo, S.; Akahama, Y.; Terada, S.; Narita, S. Jpn. J. Appl. Phys. 1982, 21 (8), L482-L484.

Letter