## Few-layer SnSe2 transistors with high on/off ratios

Tengfei Pei, Lihong Bao, Guocai Wang, Ruisong Ma, Haifang Yang, Junjie Li, Changzhi Gu, Sokrates Pantelides , Shixuan Du, and Hong-jun Gao

Citation: Applied Physics Letters **108**, 053506 (2016); doi: 10.1063/1.4941394 View online: http://dx.doi.org/10.1063/1.4941394 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/108/5?ver=pdfcov Published by the AIP Publishing

Articles you may be interested in Field-effect transistors of high-mobility few-layer SnSe2 Appl. Phys. Lett. **109**, 203104 (2016); 10.1063/1.4967744

2D-2D tunneling field-effect transistors using WSe2/SnSe2 heterostructures Appl. Phys. Lett. **108**, 083111 (2016); 10.1063/1.4942647

High-performance ZnO nanowire field-effect transistor with forming gas treated SiO2 gate dielectrics J. Appl. Phys. **117**, 164308 (2015); 10.1063/1.4919220

SnSe2 field-effect transistors with high drive current Appl. Phys. Lett. **103**, 263104 (2013); 10.1063/1.4857495

Field effect transistors with layered two-dimensional SnS2-xSex conduction channels: Effects of selenium substitution Appl. Phys. Lett. **103**, 093108 (2013); 10.1063/1.4819072

## Few-layer SnSe<sub>2</sub> transistors with high on/off ratios

Tengfei Pei,<sup>1</sup> Lihong Bao,<sup>1,a)</sup> Guocai Wang,<sup>1</sup> Ruisong Ma,<sup>1</sup> Haifang Yang,<sup>1</sup> Junjie Li,<sup>1</sup> Changzhi Gu,<sup>1</sup> Sokrates Pantelides,<sup>2,3</sup> Shixuan Du,<sup>1</sup> and Hong-jun Gao<sup>1</sup> <sup>1</sup>Institute of Physics, Chinese Academy of Sciences, P. O. Box 603, Beijing 100190, China <sup>2</sup>Department of Physics and Astronomy, Vanderbilt University, Nashville, Tennessee 37235, USA <sup>3</sup>Material Science and Technology Division, Oak Ridge National Laboratory, Oak Ridge, Tennessee 37381, USA

(Received 25 December 2015; accepted 20 January 2016; published online 5 February 2016)

We report few-layer  $SnSe_2$  field effect transistors (FETs) with high current on/off ratios. By trying different gate configurations, 300 nm SiO<sub>2</sub> and 70 nm HfO<sub>2</sub> as back gate only and 70 nm HfO<sub>2</sub> as back gate combined with a top capping layer of polymer electrolyte, few-layer  $SnSe_2$  FET with a current on/off ratio of 10<sup>4</sup> can be obtained. This provides a reliable solution for electrically modulating quasi-two-dimensional materials with high electron density (over  $10^{13}$  cm<sup>-2</sup>) for field-effect transistor applications. © 2016 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4941394]

Graphene's success has triggered extensive research on isolation, characterization, and device applications of twodimensional (2D) layered materials.<sup>1</sup> The successful isolation and synthesis of transition-metal dichalcogenide (TMD) atomic layers such as  $MoS_2$  boosted the research on exploration of fundamentally interesting physical phenomena and technological applications in electronics and optoelectronics benefiting from their sizeable and thickness-dependent bandgaps, which are not present in graphene.<sup>2,3</sup> In TMDs, the *d* electrons are the main source to form lower valence band maxima, inducing a band transition from indirect to direct bandgap when reduced to single atomic layer.<sup>4</sup> Consequently, strong photoluminescence properties are present in single-layer TMDs.<sup>2</sup>

Recently, the demonstration of few-layer SnS<sub>2</sub> for applications in transistors,<sup>5</sup> logic circuits, and photodetectors<sup>6</sup> extends this system to dichalcogenides of metals from the main group in the periodic table of the elements. Compared to TMDs, no d electrons are involved in the bonding configuration of these metal dichalcogenides. As a result, new phenomena emerge. For example, the bandgap gets smaller for SnS<sub>2</sub> when reducing the thickness from bulk to monolayer, which is contrary to that of TMDs.<sup>7</sup> As a close relative, fewlayered SnSe<sub>2</sub> with similar band structure has been rarely investigated.<sup>8</sup> Previous attempts on SnSe<sub>2</sub> field effect transistors (FETs) indicated that the current cannot be completely turned off due to the high electron density in SnSe<sub>2</sub> layers  $(10^{18} \text{ cm}^{-3} \text{ in bulk SnSe}_2, 9 \text{ compared with } \sim 10^{16} \text{ cm}^{-3} \text{ in}$  $MoS_2^{10}$  and  $\sim 10^{15} cm^{-3}$  in black phosphorus<sup>11</sup>). Therefore, how to effectively modulate the transport of carriers remains a challenge for FET applications of such systems. Pan et al. have investigated the effect of selenium substitution for sulfur in 2D  $SnS_2$  with thickness in the range of 11–35 nm.<sup>12</sup> When sulfur is completely replaced with selenium, SnSe<sub>2</sub> transistors cannot be turned off. This feature was also confirmed by Su et al., in whose devices the thickness of SnSe<sub>2</sub> is about 84 nm.<sup>13</sup> The main challenge to modulate SnSe<sub>2</sub> transistors comes from the high electron concentration in  $SnSe_2$  and the difficulty in reducing the thickness of flakes.

In this study, we investigate FETs based on mechanically exfoliated few-layered  $\text{SnSe}_2$  flakes. We found that, when 300 nm SiO<sub>2</sub> or 70 nm HfO<sub>2</sub> on a p<sup>++</sup> Si substrate are used as back-gate dielectrics, the SnSe<sub>2</sub> FETs cannot be turned off. On the other hand, a combination of 70 nm HfO<sub>2</sub> as back gate with a top capping layer of polymer electrolyte, the SnSe<sub>2</sub> FETs show a high current on/off ratio over 10<sup>4</sup>. Our findings demonstrate a reliable way to electrically modulate the 2D materials with high carrier density, which is promising for extending such systems to electronic device applications.

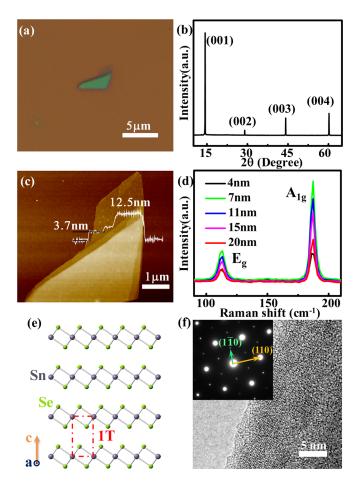

At first, few-layered SnSe<sub>2</sub> flakes are mechanically exfoliated onto a p<sup>++</sup> Si substrate covered with 300 nm SiO<sub>2</sub> using a Scotch tape. Compared with that of MoS<sub>2</sub>, the contrast of SnSe<sub>2</sub> flakes is much weaker. Figure 1(a) shows an optical micrograph of a typical exfoliated SnSe<sub>2</sub> flake. The thinnest part of the flake with a thickness of 3.7 nm is almost invisible when illuminated with white light. Due to this difficulty, we have never obtained or observed monolayer SnSe<sub>2</sub>. X-ray diffraction (XRD) characterization indicates that the SnSe<sub>2</sub> crystal can be indexed as CdI<sub>2</sub>-type layered structure (JCPDS No. 89-2939), shown in Figure 1(b). The inter-plane distance along the  $\langle 001 \rangle$ direction is 6.14 Å.

In previous studies, a thickness-dependent Raman spectrum has been frequently observed in 2D TMDs materials, where the out-of-plane  $A_{1g}$  mode shows a blue shift with increasing thickness due to the stiffening of the out-of-plane phonons; on the other hand, the in-plane degenerate  $E_g$  mode shows a red shift upon the addition of extra layers due to the relaxation of in-plane bonding.<sup>14</sup> However, for SnSe<sub>2</sub> flakes with different thicknesses, the Raman spectra of the out-of-plane  $A_{1g}$  mode at  $187 \text{ cm}^{-1}$  and in-plane  $E_g$  mode at  $112 \text{ cm}^{-1}$  do not show any thickness-dependent features, as shown in Figure 1(d). Similar to MoS<sub>2</sub>, the thickness-dependent feature disappears when it is beyond five layers.<sup>14</sup> In fact, there are two kinds of CdI<sub>2</sub>-type stacking orders in SnSe<sub>2</sub> crystals, 1T and 6Hb polytypes.<sup>15,16</sup> Both of their out-of-plane  $A_{1g}$  modes are located near 185 cm<sup>-1</sup> and in-plane

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: lhbao@iphy.ac.cn

FIG. 1. (a) Optical micrograph and (c) atomic force microscopy (AFM) image of a SnSe<sub>2</sub> flake. (b) The XRD pattern of the bulk SnSe<sub>2</sub> crystal. (d) Raman spectra of SnSe<sub>2</sub> with different thickness. (e) Atomic stack schematics of 1 T SnSe<sub>2</sub> projected along [100] direction. (f) HRTEM image of SnSe<sub>2</sub>. Inset: Selected-area electron diffraction (SAED) of SnSe<sub>2</sub> along [001] zone axis. Yellow arrow represents crystal plane (110) with interplanar spacing of 1.9 Å, and green arrow represents crystal plane (11 $\overline{10}$ ) with interplanar spacing of 3.3 Å.

$E_g$  modes located around  $110 \text{ cm}^{-1}$ , making it quite difficult to identify the special polytype just based on the Raman or XRD pattern. Selected-area electron diffraction (SAED) and transmission electron microscopy (TEM) of SnSe<sub>2</sub> crystal are shown in Figure 1(f), where diffraction spots from {110} and {110} planes are present. Because the diffraction spots from crystal planes {110} are forbidden in 6Hb type SnSe<sub>2</sub>, the structure of SnSe<sub>2</sub> in our study can be identified as 1 T polytype.

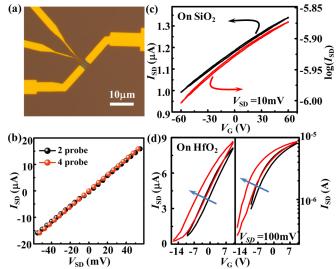

SnSe<sub>2</sub> FETs are fabricated by a standard electron-beam lithography technique followed by deposition of Cr/Au (6/60 nm) in sequence as contact electrodes. All electrical characterizations are performed at room temperature in a vacuum chamber with pressure lower than  $10^{-5}$ Torr, and the electrical properties are measured using a Keithley 4200-SCS system. A representative optical photograph of a SnSe<sub>2</sub> FET is shown in Figure 2(a). To evaluate the contact resistance, both two-and four-probe measurements are performed. As shown in Figure 2(b), a good linear relationship between the current and bias voltage indicates a good Ohmic contact between Cr/Au electrodes and the interface of SnSe<sub>2</sub>. Moreover, the coincidence between two- and four-probe measurements suggests a low contact resistance.

FIG. 2. (a) Optical microscopy image of a few-layer  $SnSe_2$  transistor. (b) Four- and two-probe *I-V* curves of a few-layer  $SnSe_2$  transistor.(c) Transfer characteristic of a few-layer  $SnSe_2$  with 300 nm SiO<sub>2</sub> as the gate insulator. (d) Transfer characteristics of a few-layer  $SnSe_2$  with 70 nm HfO<sub>2</sub> as the gate insulator, which move backward with the increase in sweeping scope.

Figure 2(c) presents the transfer curve of the SnSe<sub>2</sub> FET based on 300 nm SiO<sub>2</sub> as dielectric insulator. When we sweep the back-gate voltage  $V_G$  from -60 V to +60 V and back sweep it from +60 V to -60 V, the few-layered SnSe<sub>2</sub> exhibits an n-type conduction behavior with an electron mobility about 41 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, extracted from  $\mu = [L/(WC_iV_{SD})]$  $\times [dI_{SD}/dV_G]$ , where L and W are channel length and width, respectively, and  $C_i$  is the capacitance per unit area of back gate insulator. The obtained electron mobility (41 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) in our device is almost five times higher than a previous report (8.6 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>).<sup>13</sup> However, the current cannot be completely turned off even by increasing the gate voltage to -100 V. No apparent hysteresis behavior is present in the transfer curves, indicating a fully capacitive coupling and low interface defect density between the interface of SnSe<sub>2</sub> and SiO<sub>2</sub>.

We can derive the threshold voltage  $V_{\rm T}$  by extrapolation of the linear part of the transfer curve according to the equation:  $I_{SD} = (WC_iV_{SD}/L) \times (V_G - V_T)$ . The  $V_T$  of the device on  $SiO_2$  is about -305 V. We can calculate the area density of electrons in the SnSe<sub>2</sub> flake by  $Q = C_{SiO_2} \cdot V_T / e$ , about  $2.2 \times 10^{13} \text{ cm}^{-2}$ , where  $C_{SiO_2} = 11.5 \text{ nF cm}^{-2}$ . It is too high to modulate with 300 nm SiO<sub>2</sub> as dielectric medium. To deplete the excess electrons in SnSe<sub>2</sub>, we further adopt 70 nm HfO<sub>2</sub> as the back gate insulator. The  $HfO_2$  is deposited onto  $p^{++}$  Si substrate by atomic layer deposition (ALD). As shown in Figure 2(d), the current on/off ratio is just beyond  $10^1$ , even though the dielectric constant of  $HfO_2$  (25) is 6 times higher than that of  $SiO_2$  (3.9).<sup>17</sup> If we consider the SnSe<sub>2</sub> channel as 2D electron gas with area carrier density  $2.2 \times 10^{13}$  cm<sup>-2</sup>, the threshold voltage is determined as -11.1 V by  $V_T = eQ/$  $C_{HfO_2}(C_{HfO_2} = 316 \,\mathrm{nF \, cm^{-2}})$ . From the transfer curve in Figure 2(d), we can obtain the threshold voltage to be between -12.5 V and -10.7 V, which is consistent with the above assumption. However, when sweeping  $V_{\rm G}$  from  $-16\,{\rm V}$  to 10 V, unexpectedly, the device does not turn off at -11 V.

Therefore, it is unreasonable to simply consider the electron distribution in the SnSe<sub>2</sub> flake as 2D electron gas. There should be electrical potential difference along the vertical direction. According to semiconductor theory, if we want to deplete the excess electrons in the semiconductor, for the metal-insulator-semiconductor (MIS) structure, the thickness of the channel materials should be thinner than its maximum depletion width  $W_{\rm Dm}$ , which is determined as<sup>18</sup>

$$W_{\rm Dm} \approx \left(\frac{2\varepsilon_r \varepsilon_0 \psi_{inv}}{eN_{\rm D}}\right)^{1/2},$$

(1)

where  $\psi_{inv}$  is the surface potential when strong inversion occurs,  $N_D$  is the donor impurity concentration,  $\varepsilon_0$  and  $\varepsilon_r$  represent vacuum and relative permittivity, respectively. For SnSe<sub>2</sub>, because of the shallow donor energy level, which is less than 25 meV below the conduction band,<sup>12,13</sup>  $\psi_{inv}$  equals to the band gap (about 1 V) and  $N_D$  is equal to the electron density of SnSe<sub>2</sub> at room temperature, about  $2.2 \times 10^{19}$  cm<sup>-3</sup> (thickness ~10 nm). The permittivity of SnSe<sub>2</sub> along the c axis,  $\varepsilon_r$ , is about 10.<sup>19</sup> Therefore,  $W_{Dm}$  of SnSe<sub>2</sub> is about 7 nm, which is smaller than the thickness of the flake. Naturally, there is no way to deplete the electrons only by the back gate modulation, regardless of how large the capacitance of the gate insulator is.

A natural way to modulate the transport of carriers in FETs is to apply a top gate using high-k dielectrics when the modulation of the back gate is not so effective. Therefore, we introduced a top gate to control the transporting electrons on the top surface of the  $SnSe_2$  device. A high-k top gate dielectric is fabricated by atomic layer deposition of HfO<sub>2</sub>. However, the SnSe<sub>2</sub> cannot survive under the "harsh" deposition conditions. Even when we lower the deposition temperature to 150°C, the conductivity of the SnSe<sub>2</sub> still increases at least two orders of magnitude after the deposition. Another widely used technique in tuning the transport of carriers in FETs is the use of an electrochemical gate (including ionic liquid and ion gel). It is much more effective than back gate (SiO<sub>2</sub>) and polar-dielectric-based top gate (HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, etc.), due to the formation of ultra-thin  $(\sim 1 \text{ nm})$  double layer of ions, compared to that of back gate  $(\sim 300 \text{ nm})$  and polar-dielectric-based top gate (>5 nm).<sup>20,21</sup>

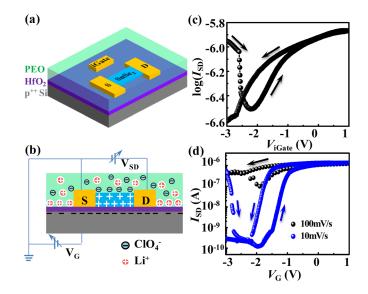

Here, we further adopt ionic polymer electrolyte as the top capping material in combination with  $70 \text{ nm HfO}_2$  on  $p^{++}$  Si substrate as back gate. The polymer electrolyte is applied by spin coating with filtered (pore size 500 nm) anhydrous methanol solution of polyethylene oxide (PEO) containing 20 wt. % LiClO<sub>4</sub>.<sup>22</sup> Then, it is annealed at 100 °C for half an hour in vacuum (50 Pa) to evaporate the solvents and solidify the electrolyte. A schematic diagram of such device is presented in Figure 3(a). Figure 3(c) gives the representative transfer curve of the SnSe<sub>2</sub> FET under the modulation of ionic polymer electrolyte as top gate (iGate). Similar to the result of back gate in Figure 2(d), the current on/off ratio is about 1, and the device is not turned off completely by the iGate modulation, in spite of the high capacitance of the polymer electrolyte (above  $1 \,\mu F \,cm^{-2}$ ).<sup>23</sup> However, with the covered polymer electrolyte, the current on/off ratio of a SnSe<sub>2</sub> transistor increases from  $10^1$  to  $10^4$ using only back gate modulation, as shown in Figure 3(d). The sweeping rate of the voltage is 10 mV/s. If we increase the sweeping rate to 100 mV/s, the high on/off ratio also

FIG. 3. (a) Schematic diagram of the geometry of  $SnSe_2$  transistor covered with polymer electrolyte using 70 nm HfO<sub>2</sub>/p<sup>++</sup>Si as back gate. (b) Schematic of charge accumulation by the EDL formed at the interfaces of PEO with HfO<sub>2</sub> and the top surface of  $SnSe_2$  during gate bias sweeping. (c) Transfer characteristic of polymer electrolyte top gated  $SnSe_2$  transistor. (d) Transfer characteristics of a 70 nm HfO<sub>2</sub> back gated  $SnSe_2$  covered with polymer electrolyte measured at different sweeping rates. The iGate is disconnected.

disappears, indicating that there is ionic migration during the turn-off process.

Since there is only a back gate voltage bias applied during the measurement in Figure 3(d), what role of the capping polymer electrolyte plays in tuning the transport of carriers in SnSe<sub>2</sub> FET remains a question. The leakage current between iGate and back gate is below  $10^{-10}$ A, suggesting no short circuit occurs. A simple model considering the series capacitance of the HfO<sub>2</sub> insulator and the polymer electrolyte is schematically shown in Figure 3(b). When the back gate is biased, an electrical double layer (EDL) is formed on the surface of HfO<sub>2</sub> near the device, which actually functions same as the iGate and induces the formation of an EDL with opposite charged inner Helmholtz plane on the top surface of SnSe<sub>2</sub> flakes. When the negative back gate voltage is applied,  $Li^+$  ions gather on the HfO<sub>2</sub> surface near the flake and  $ClO_4^-$  assembles on the top surface of  $SnSe_2$  flake, which deplete the electrons existing on the top surface of SnSe2 and the immobile ionized donors with positive charges are remained. With the help of the polymer electrolyte, the maximum thickness of SnSe<sub>2</sub> flakes that can be modulated by the field-effect configuration increase from 7 nm to 14 nm, which covers the thickness scope of the flakes we used.

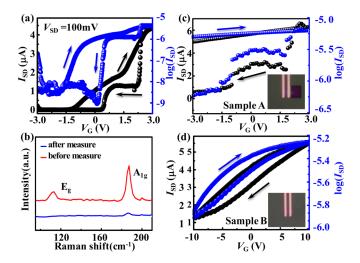

Additionally, when we increase the back gate voltage over 1 V, the current  $I_{SD}$  increases further and a turning point appears near 1.5 V, as shown in Figure 4(a). However, during the backward sweeping,  $I_{SD}$  does not decrease continuously but with steps. After the sweeping loop, the conductivity decreases three orders of magnitude. Repeating such a loop finally results in the death of the device. In Figure 4(b), Raman spectra are recorded both before and after the large positive gate bias. After the measurement, the peaks of vibration modes  $E_g$  and  $A_{1g}$  almost disappear, revealing an

FIG. 4. (a) Transfer characteristic of 70 nm HfO<sub>2</sub> SnSe<sub>2</sub> cover with polymer electrolyte when gate bias sweeping from -3 V to 3 V. (b) Raman spectra of the device in (a) before and after the transfer characteristic measurement. (c) Transfer characteristic of device partly protected with PMMA, with active area is covered by PMMA and a corner is exposed to polymer electrolyte, named sample A. (d) Transfer characteristic of device fully covered by PMMA, labeled as sample B.

irreversible structural transition has occurred in the SnSe<sub>2</sub> flake. One possible origin of this transition is that Li<sup>+</sup> ions intercalate into the interlayer of SnSe<sub>2</sub> at large positive gate bias. To confirm this, we conducted the following control experiments.<sup>24</sup> In Figure 4(c), the active area of the sample A is covered by a layer of poly(methyl methacrylate) (PMMA) (300 nm) with the side corner exposed to the polymer electrolyte. The control sample B is fully protected by PMMA, as shown in Figure 4(d). Similar to the device with active area fully exposed to the polymer electrolyte, sample A also shows a stepped drop when the gate bias decreases from 3 V, indicating the diffusion of Li<sup>+</sup> ions happens when the gate bias reaches 3 V. Therefore, the degradation process is directly related to the Li<sup>+</sup> intercalation. Although the Li<sup>+</sup>-ion intercalation can be sustained with a large positive gate bias, it becomes unstable when the gate bias decreases. Different from the  $TaS_2$  flakes, the  $Li^+$  ions cannot de-intercalate from the  $SnSe_2$  flakes reversibly. When Li<sup>+</sup> ions de-intercalate, the structure of SnSe<sub>2</sub> flakes is destroyed. This causes the conductivity to decrease step by step. In lithium-ion batteries based on SnSe<sub>2</sub> as anode material, the discharge performance also degrades after several chargedischarge cycles, which implies the instability of SnSe<sub>2</sub> during the Li<sup>+</sup> intercalation.<sup>2</sup>

In conclusion, different gate configurations, 300 nm SiO<sub>2</sub>, 70 nm HfO<sub>2</sub>, and 70 nm HfO<sub>2</sub> combined with a polymer electrolyte, are used to modulate the transport behavior of few-layered SnSe<sub>2</sub> FETs. The current on/off ratio can be improved to  $10^4$  by using 70 nm HfO<sub>2</sub> as back-gate dielectric in combination with a layer of polymer electrolyte. Our results demonstrate a reliable way to modulate other quasi-2D systems with electron density over  $10^{13} \text{ cm}^{-2}$  and thickness about 10 nm.

This work was supported by National Natural Science Foundation of China (Grant Nos. 61474141 and 61335006), National "973" Projects of China (Grant No. 2013CBA01600), the Chinese Academy of Sciences (CAS), and Youth Innovation Promotion Association of CAS (20150005). The authors would like to thank the Analysis and Test Center in Technical Institute of Physics and Chemistry for the help in electrical characterization of the field-effect transistors.

- <sup>1</sup>K. S. Novoselov, D. Jiang, F. Schedin, T. J. Booth, V. V. Khotkevich, S. V. Morozov, and A. K. Geim, Proc. Natl. Acad. Sci. U. S. A. **102**(30), 10451 (2005).

- <sup>2</sup>A. Splendiani, L. Sun, Y. Zhang, T. Li, J. Kim, C.-Y. Chim, G. Galli, and F. Wang, Nano Lett. **10**(4), 1271 (2010).

- <sup>3</sup>K. F. Mak, C. Lee, J. Hone, J. Shan, and T. F. Heinz, Phys. Rev. Lett. **105**(13), 136805 (2010).

- <sup>4</sup>Q. H. Wang, K. Kalantar-Zadeh, A. Kis, J. N. Coleman, and M. S. Strano, Nat. Nanotechnol. 7(11), 699 (2012).

- <sup>5</sup>H. S. Song, S. L. Li, L. Gao, Y. Xu, K. Ueno, J. Tang, Y. B. Cheng, and K. Tsukagoshi, Nanoscale 5(20), 9666 (2013).

- <sup>6</sup>G. Su, V. G. Hadjiev, P. E. Loya, J. Zhang, S. Lei, S. Maharjan, P. Dong, P. M. Ajayan, J. Lou, and H. Peng, Nano Lett. **15**(1), 506 (2015).

- <sup>7</sup>Y. Huang, E. Sutter, J. T. Sadowski, M. Cotlet, O. L. A. Monti, D. A. Racke, M. R. Neupane, D. Wickramaratne, R. K. Lake, B. A. Parkinson, and P. Sutter, ACS Nano 8(10), 10743 (2014).

- <sup>8</sup>J. Robertson, J. Phys. C: Solid State Phys. 12(22), 4753 (1979).

- <sup>9</sup>Non-Tetrahedrally Bonded Elements and Binary Compounds I, edited by O. Madelung, U. Rössler, and M. Schulz (Springer, Berlin, Heidelberg, 1998), Vol. 41C, Chap. 801, p. 1.

- <sup>10</sup>D. M. Dambra, J. V. Marzik, R. Kershaw, J. Baglio, K. Dwight, and A. Wold, J. Solid State Chem. 57(3), 351 (1985).

- <sup>11</sup>Non-Tetrahedrally Bonded Elements and Binary Compounds I, edited by O. Madelung, U. Rössler, and M. Schulz (Springer, Berlin, Heidelberg, 1998), Vol. 41C, Chap. 1101, p. 1.

- <sup>12</sup>T. S. Pan, D. De, J. Manongdo, A. M. Guloy, V. G. Hadjiev, Y. Lin, and H. B. Peng, Appl. Phys. Lett. **103**(9), 093108 (2013).

- <sup>13</sup>Y. Su, M. A. Ebrish, E. J. Olson, and S. J. Koester, Appl. Phys. Lett. 103(26), 263104 (2013).

- <sup>14</sup>H. Li, Q. Zhang, C. C. R. Yap, B. K. Tay, T. H. T. Edwin, A. Olivier, and D. Baillargeat, Adv. Func. Mater. 22(7), 1385 (2012).

- <sup>15</sup>D. G. Mead and J. C. Irwin, Solid State Commun. 20(9), 885 (1976).

- <sup>16</sup>A. J. Smith, P. E. Meek, and W. Y. Liang, J. Phys. C: Solid State Phys. 10(8), 1321 (1977).

- <sup>17</sup>G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. 89(10), 5243 (2001).

- <sup>18</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3rd ed. (John Wiley & Sons, Inc., Hoboken, New Jersey, 2007).

- <sup>19</sup>Non-Tetrahedrally Bonded Elements and Binary Compounds I, edited by O. Madelung, U. Rössler, and M. Schulz (Springer, Berlin, Heidelberg, 1998), Vol. 41C, Chap. 802, p. 1.

- <sup>20</sup>K. Ueno, S. Nakamura, H. Shimotani, A. Ohtomo, N. Kimura, T. Nojima, H. Aoki, Y. Iwasa, and M. Kawasaki, Nat. Mater. 7(11), 855 (2008).

- <sup>21</sup>B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, Nat. Nanotechnol. 6(3), 147 (2011).

- <sup>22</sup>M. J. Panzer, C. R. Newman, and C. D. Frisbie, Appl. Phys. Lett. 86(10), 103503 (2005).

- <sup>23</sup>A. Das, S. Pisana, B. Chakraborty, S. Piscanec, S. K. Saha, U. V. Waghmare, K. S. Novoselov, H. R. Krishnamurthy, A. K. Geim, A. C. Ferrari, and A. K. Sood, Nat. Nanotechnol. 3(4), 210 (2008).

- <sup>24</sup>Y. Yu, F. Yang, X. F. Lu, Y. J. Yan, H. C. Yong, L. Ma, X. Niu, S. Kim, Y.-W. Son, D. Feng, S. Li, S.-W. Cheong, X. H. Chen, and Y. Zhang, Nat. Nanotechnol. **10**(3), 270 (2015).

- <sup>25</sup>H. Mukaibo, A. Yoshizawa, T. Momma, and T. Osaka, J. Power Sources 119–121, 60 (2003).

- <sup>26</sup>J. Choi, J. Jin, I. G. Jung, J. M. Kim, H. J. Kim, and S. U. Son, Chem. Commun. 47(18), 5241 (2011).